Home>>HERON modular systems>>How HERON modules work together

How do the HERON modules work together?

HERON modules are designed to interface to FIFOs that are provided by the module carrier board.

For FPGA modules you use the Hardware Interface layer VHDL to access the HERON-FIFOs using dedicated FPGA hardware.

For C6000 modules you use the HERON-API software to access the HERON-FIFOs using the DMA engines of the DSP.

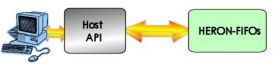

For Host (PC) programs you use the Host-API software to access the HERON-FIFOs using the master mode hardware of the module carrier card.

A HEART module carrier allows you to use those FIFOs to make connections between modules.

The FIFO connections are configured by software using the HERON Serial Bus. You define the connections you need in a simple text file, and the software tools we provide do the rest.

The FIFOs are synchronous, 32bits wide and can be clocked at 100Mhz. Each module provides its own clock so they do not need to be the same frequency or phase. The FIFO flags are used to determine when data can be transferred, so data is not lost.

Using HEART you can connect FPGA, C6000 and I/O modules in any combination, here are some examples...

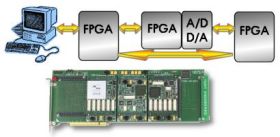

Example 1. Several FPGA modules

Different FPGA modules can be combined in the same system to get more system gates or to use the different I/O capabilities.

The FPGAs communicate by sending data through the HERON FIFOs using Hardware Interface Layer,

Optionally a PC can be part of the system, having FIFO connection(s) to the FPGA modules. A program on the PC will use Host-API to access the FIFOs.

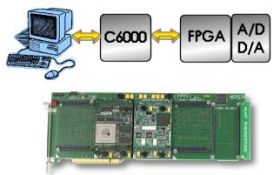

Example 2. Mix of C6000 and FPGA

A module with a C6000 DSP can be used with an FPGA module. In this case the FPGA module also

has A/D and D/A capability. The FPGA and C6000 communicate by

sending data through the HERON FIFOs. For this the C6000 uses

HERON-API and the FPGA uses Hardware interface layer.

Optionally a PC can be part of the

system, having FIFO connection(s) to the C6000 and or FPGA modules.

A program on the PC will use Host-API to access the FIFOs.

Example 3. Embedded system with FPGA plus A/Ds and D/As

FPGA modules which also have fast A/D and D/A channels directly connected to the FPGA can be used in an embedded system.

By using the on-module FLASH based PROM to boot the FPGA program the system can be used stand alone (embedded).

Example 4. System with 2 boards

Modules can be combined across more than one Module carrier using the

inter-board connection modules.

Modules can be combined across more than one Module carrier using the

inter-board connection modules.The connection between boards is used in exactly the same way as the FIFOs on a single module carrier.

Such a system can be embedded, used with both boards in the same PC, or with the 2 boards in different PCs. Perhaps one will be in a PC and the other embedded at a remote location.

Embedded and stand alone systems

Changing your HERON and HEART system is a simple process.

All of our module carriers can be used in embedded systems.

C6000 modules pre-boot from on board FLASH ROM anyway, and we provide

tools to add your own application software to that ROM for an embedded

system.

FPGA modules have a PROM (sometimes a build time option) that can hold

their configuration for an embedded system.

HEART can still be used to provide communication between modules. The

final HEART configuration can be embedded into the C6000 application

software or stored in the FPGA's configuration PROM.

For more details about Embedded Systems look here.

What performance can I get?

The data sheet performance figures of modern DSP processors make it

seem possible to approach application areas that previously could not be

approached with Digital systems. Digital Radio and the associated use of

Direct IF digitisation techniques is one such area.

System designers must, however, consider all aspects of the system, not

simply the MIPs or MFLOPS ratings. With a HERON system the I/O can be

tightly integrated with the processing. HEART can provide data transfer

rates between nodes of up to 400Mbytes/sec. However, other aspects of the

system are likely to impose a lower limit on the performance. Consider,

for example, issues like the fact that a C6000 memory bus will be used for

I/O data as well as instructions and processing results. Another common

limit is if the host PC is used as a node in the system -- here peak rates

can only be approached if there is a buffer used to decouple the "bursty"

nature of PCI transfers in a PC. See here for a more complete discussion.

For more detailed information about Hunt Engineering technology see the Technology section.