Home>>Products>>IP for HERON-FPGA modules>>Filter Demo

Filter Demo/Development Framework

The tutorial is really aimed at learning how to use the Xilinx Core Generator. It discusses how to design and implement a digital (FIR) filter using an FPGA.

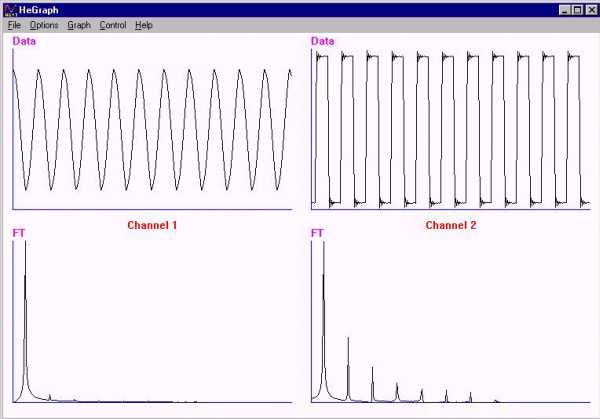

This demonstration can be run using a HEPC9 or HERON-BASE2 module carrier, using a HERON-IO2V without re-compiling. It would be easy to recompile it to use with another HERON-IO module, or perhaps the combination of a HERON-FPGA module with a separate Analogue I/O module. The FPGA performs the filtering at the full sample rate (100Mhz with the HERON-IO2) and finally uses the Hardware Interface Layer to put the results into a HERON FIFO. The Host API is used to receive the results using a graph program running on the host PC.

The demo demonstrates communicating between an FPGA and the PC, and drawing a graph on the PC screen as well as using an FPGA to make a filter.