Home>>Products>>IP for HERON-FPGA modules>>DDC Demo

DDC Demo/Development Framework

This demo/framework for a HERON-IO2V or a HERON-IO5V uses an example implementation of a DDC to show you how to design and build a Digital Down Converter (DDC) using blocks from the Xilinx Core Generator. It discusses how to design and implement a DDC, but also shows that the Core Generator DDC block can often be used to perform the whole task.

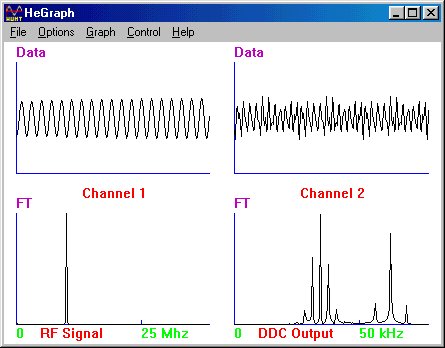

This demonstration can be run using a HEPC9 module carrier, using a HERON-IO2V or a HERON-IO5V without re-compiling. It would be easy to recompile it to use with another HERON-IO module, or perhaps the combination of a HERON-FPGA module with a separate Analogue I/O module. The FPGA outputs a modulated signal on its DAC outputs, and digitising that signal, performs the DDC function and outputs baseband data to the HERON FIFO using the Hardware Interface Layer. There is a multiplexor controlled by the Heron Serial Bus that allows you to view the signal at various points along the processing pipeline. This helps you to better understand the operation of the DDC. The Host API is used to receive the results using a graph program running on the host PC.

The demo demonstrates communicating between an FPGA and the PC, using the Heron Serial Bus to control FPGA logic and drawing a graph on the PC screen as well as using an FPGA to make a DDC.