#### **HUNT ENGINEERING**

Chestnut Court, Burton Row, Brent Knoll, Somerset, TA9 4BP, UK Tel: (+44) (0)1278 760188,

Fax: (+44) (0)1278 760199, Email: sales@hunteng.co.uk http://www.hunteng.co.uk http://www.hunt-dsp.com

# HUNT ENGINEERING HERON-FPGA5

HERON Module with Virtex II 1M gate FPGA, and 256Mbytes of SDRAM

# USER MANUAL

Hardware Rev A

Document Rev E

R.Williams 05/05/05

This documentation and the product it is supplied with are Copyright HUNT ENGINEERING 2003. All rights reserved. HUNT ENGINEERING maintains a policy of continual product development and hence reserves the right to change product specification without prior warning.

#### WARRANTIES LIABILITY and INDEMNITIES

HUNT ENGINEERING warrants the hardware to be free from defects in the material and workmanship for 12 months from the date of purchase. Product returned under the terms of the warranty must be returned carriage paid to the main offices of HUNT ENGINEERING situated at BRENT KNOLL Somerset UK, the product will be repaired or replaced at the discretion of HUNT ENGINEERING.

Exclusions - If HUNT ENGINEERING decides that there is any evidence of electrical or mechanical abuse to the hardware, then the customer shall have no recourse to HUNT ENGINEERING or its agents. In such circumstances HUNT ENGINEERING may at its discretion offer to repair the hardware and charge for that repair.

Limitations of Liability - HUNT ENGINEERING makes no warranty as to the fitness of the product for any particular purpose. In no event shall HUNT ENGINEERING'S liability related to the product exceed the purchase fee actually paid by you for the product. Neither HUNT ENGINEERING nor its suppliers shall in any event be liable for any indirect, consequential or financial damages caused by the delivery, use or performance of this product.

Because some states do not allow the exclusion or limitation of incidental or consequential damages or limitation on how long an implied warranty lasts, the above limitations may not apply to you.

#### **TECHNICAL SUPPORT**

Technical support for HUNT ENGINEERING products should first be obtained from the comprehensive Support section <a href="http://www.hunteng.co.uk/support/index.htm">http://www.hunteng.co.uk/support/index.htm</a> on the HUNT ENGINEERING web site. This includes FAQs, latest product, software and documentation updates etc. Or contact your local supplier - if you are unsure of details please refer to <a href="http://www.hunteng.co.uk">http://www.hunteng.co.uk</a> for the list of current re-sellers.

HUNT ENGINEERING technical support can be contacted by emailing support@hunteng.demon.co.uk, calling the direct support telephone number +44 (0)1278 760775, or by calling the general number +44 (0)1278 760188 and choosing the technical support option.

#### Version

- A initial document

- B minor typographical corrections

- C updated 'How to Make a New Design' section

- D HERON-FPGA5 version 2 introduced

- E updated 'How to Make a New Design' section to reference external document

# **TABLE OF CONTENTS**

| INTRODUCTION                                        | 5  |

|-----------------------------------------------------|----|

| PHYSICAL LOCATION OF ITEMS ON THE HERON-FPGA5       | 7  |

| GETTING STARTED                                     | 8  |

| STANDARD INTELLECTUAL PROPERTY (IP)                 | 8  |

| MODULE FEATURES                                     | g  |

| SERIAL CONFIGURATION OF THE USER FPGA               |    |

| USER FPGA BOOT ROM                                  |    |

| CLOCKING OF THE FPGA                                |    |

| HERON FIFOS                                         | 11 |

| SDRAM                                               | 12 |

| DIGITAL I/O                                         |    |

| MODULE AND CARRIER ID                               |    |

| GENERAL PURPOSE LEDS                                | 13 |

| DONE LEDS                                           |    |

| SERIAL PORTS                                        | 13 |

| GETTING STARTED ON YOUR FPGA DESIGN                 | 14 |

| Working through Example 1                           |    |

| Preparing ISE                                       |    |

| Copying the examples from the HUNT ENGINEERING CD   |    |

| Opening the Example1 Project                        |    |

| The Project's functional parameters                 |    |

| Setting up the Configuration Package                |    |

| User Timing Constraints                             |    |

| Creating the Bitstream for Example 1                |    |

| Simulating the Complete Design                      | 20 |

| MAKING YOUR OWN FPGA DESIGN                         | 21 |

| USER_AP INTERFACE                                   |    |

| HARDWARE INTERFACE LAYER                            |    |

| IMPORTANT!                                          |    |

| OTHER EXAMPLES.                                     |    |

| HOW TO MAKE A NEW DESIGN                            |    |

| Inserting your own Logic                            |    |

| Top-level Fine Tuning (using other special IO pins) |    |

| User Timing Constraints                             |    |

| HINTS FOR FPGA DESIGNS                              |    |

| Possible Sources of Clocks                          |    |

| Flow Control.                                       |    |

| Pipeline Length or "latency"                        |    |

| I/O FROM THE FPGA                                   |    |

| DSP WITH YOUR FPGA.                                 |    |

|                                                     |    |

| SOFTWAREFPGA DEVELOPMENT TOOL                       |    |

| DESIGN FILES FOR THE FPGA                           |    |

| GENERATING DESIGN FILES.                            |    |

| Files for HERON Utility (*.rbt)                     |    |

| Files for PROMs (*.mcs)                             |    |

| HERON FPGA CONFIGURATION TOOL                       |    |

| HINT ENGINEERING HOST-API                           | 33 |

| HUNT ENGINEERING HERON-API                                        | 33 |

|-------------------------------------------------------------------|----|

| HARDWARE DETAILS                                                  | 34 |

| HERON MODULE TYPE                                                 |    |

| HARDWARE RESET                                                    |    |

| SOFTWARE RESET (VIA SERIAL BUS)                                   |    |

| Config                                                            |    |

| DEFAULT ROUTING JUMPERS                                           |    |

| PHYSICAL DIMENSIONS OF THE MODULE                                 |    |

| POWER REQUIREMENTS OF THE HERON-FPGA5                             |    |

| FPGA POWER CONSUMPTION/DISSIPATION                                |    |

| FIFOS                                                             |    |

| SDRAM                                                             |    |

| USER FPGA CLOCKING                                                |    |

| User Oscillators                                                  |    |

| DIGITAL I/O CONNECTORS                                            |    |

| Using Digitally Controlled Impedance (DCI)                        |    |

| "DIGITAL I/O n" Connector Type                                    |    |

| "DIGITAL I/O n" Connector Type" "DIGITAL I/O n" Connector Pin-out |    |

| Differential PairsDifferential Pairs                              |    |

| Resistor Packs                                                    |    |

| Voltage Levels.                                                   |    |

| Differential Termination                                          |    |

| ESD Protection                                                    |    |

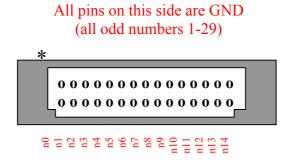

| SERIAL I/O CONNECTOR                                              |    |

| Connector Type                                                    |    |

| Connector Pin-out                                                 |    |

| Use of the MAX3160                                                |    |

| ESD protection                                                    |    |

| USING THE JTAG PROGRAMMABLE CONFIGURATION PROM                    | 48 |

| BOOT FROM PROM JUMPER                                             |    |

| UNCOMMITTED MODULE INTERCONNECTS                                  | 49 |

| GENERAL PURPOSE LEDS                                              | 49 |

| OTHER HERON MODULE SIGNALS                                        | 49 |

| FITTING MODULES TO YOUR CARRIER                                   | 50 |

| ACHIEVABLE SYSTEM THROUGHPUT                                      | 51 |

| FIFO THROUGHPUT                                                   |    |

| SDRAM THROUGHPUT                                                  |    |

|                                                                   |    |

| FROUBLESHOOTING                                                   |    |

| Hardware                                                          |    |

| SOFTWARE                                                          | 52 |

| CE MARKING                                                        | 53 |

| ΓECHNICAL SUPPORT                                                 |    |

| APPENDIX 1 – HERON SERIAL BUS COMMANDS                            |    |

| MODULE ADDRESSMODULE ADDRESS                                      |    |

| MODULE ADDRESS                                                    |    |

| FPGA CONFIGURATION                                                |    |

| USER I/O                                                          |    |

|                                                                   |    |

| APPENDIX 2 FPCA PINOUT FOR DEVELOPMENT TOOLS                      | 57 |

The HERON module is a module defined by HUNT ENGINEERING to address the needs of our customers for real-time DSP systems. The HERON module is defined both mechanically and electrically by a separate HERON module specification that is available from the HUNT ENGINEERING CD, via the user manuals section from the CD browser, or online from <a href="http://www.hunteng.co.uk">http://www.hunteng.co.uk</a> and going to the application notes section in the user area.

The HERON module specification also defines the features that a HERON module carrier must provide. HERON stands for Hunt Engineering ResOurce Node, which tries to make it clear that the module is not for a particular processor, or I/O task, but is intended to be a module definition that allows "nodes" in a system to be interconnected and controlled whatever their function. In this respect it is not like the TIM-40 specification which was specific to the 'C4x DSP.

As the HERON-FPGA5 was developed, HUNT ENGINEERING have already developed HERON modules carriers like the HEPC9, HERON processor modules (that carry various other members of the TMS320C6000 family of DSP processors from TI), and HERON-IO modules. In addition to these modules, the HERON specification is a super-set of the pre-existing HUNT ENGINEERING GDIO module, so the GDIO modules from our 'C4x product range can also be used in HERON systems.

The HERON module connects to the carrier board through several standard interfaces.

- The first is a FIFO input interface, and a FIFO output interface. This is to be used for the main inter-node communications. (It is usually also used for connection to the HOST computer if any).

- The second is an asynchronous interface that allows registers etc to be configured from a HERON module. This is intended for configuring communication systems, or perhaps to control some function specific peripherals on the carrier board.

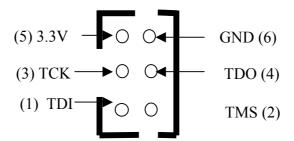

- The third is a JTAG (IEEE 1149.1) interface for running processor debug tools.

- The fourth is the HERON Serial Bus, used for configuration messages.

- The last is the general control such as reset, power etc.

HUNT ENGINEERING defined the HERON modules in conjunction with HEART – the Hunt Engineering Architecture using Ring Technology. This is a common architecture that we will adopt for our HERON carriers that provides good real time features such as low latency and high bandwidth, along with software reconfigurability of the communication system, multicast, multiple board support etc., etc.

However, it is not a requirement of a HERON module carrier that it implements such features. In fact our customers could develop their own module carrier and add our HERON modules to it. Conversely our customers could develop application specific HERON modules themselves and add them to our systems.

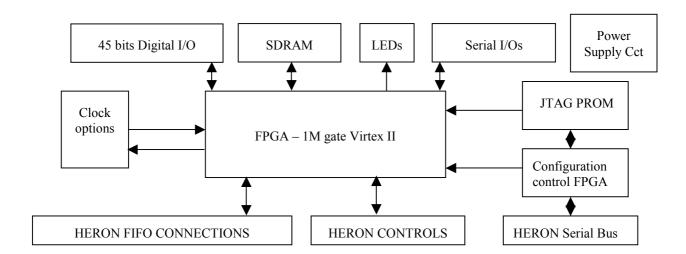

The HERON-FPGA5 is HERON module that can be used for hardware signal processing or for flexible I/O.

The HERON-FPGA5 provides a Virtex II 1M gate FPGA (Xilinx part number xc2v1000-4fg456). For more part information refer to the Xilinx web site at <a href="http://www.xilinx.com">http://www.xilinx.com</a>

The HERON-FPGA5 connects all of the HERON module signals, except JTAG, to the FPGA, allowing flexible use of the module's resources.

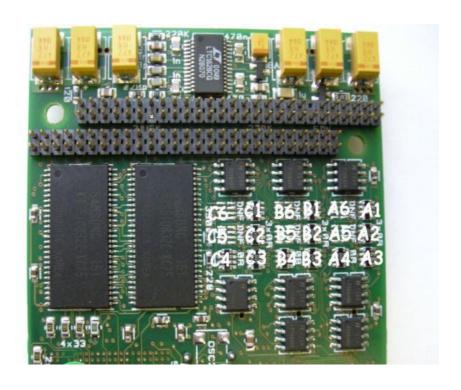

The HERON-FPGA5 provides 256Mbytes of SDRAM, directly connected to the pins of the Xilinx FPGA. This memory can be used as general purpose memory by the FPGA to perform whatever storage function is required by the users design.

The HERON-FPGA5 also provides some of the FPGA I/Os connected to connectors on the module. This allows the FPGA to be configured for a variety of I/Os. There are also configurable components that provide RS232 and RS485. A dedicated differential PECL connection is supplied which for example would allow the connecting of an FPDP interface to the FPGA.

The HERON-FPGA5 uses the HERON module's serial bus to download configuration bit-streams into the FPGA, allowing the user to configure it with standard functions provided by HUNT ENGINEERING or functions that they have developed themselves using the Xilinx development tools. It is also possible for the module to configure the FPGA from a PROM. This is intended to simplify the deployment of systems after the FPGA functions have been fully developed.

Starting from Serial number J013 the SDRAM manufacturer introduced a new SDRAM part that requires different bank management. This is taken care of inside the Hardware Interface Layer supplied, but care must be taken to use the correct HIL with the correct modules. Modules J001 to J012 inclusive are Version 1 and should use the FPGA5V1 H.I.L., modules from J013 onwards are version 2 and should use the FPGA5V2 H.I.L. Users FPGA code is unchanged by this version change.

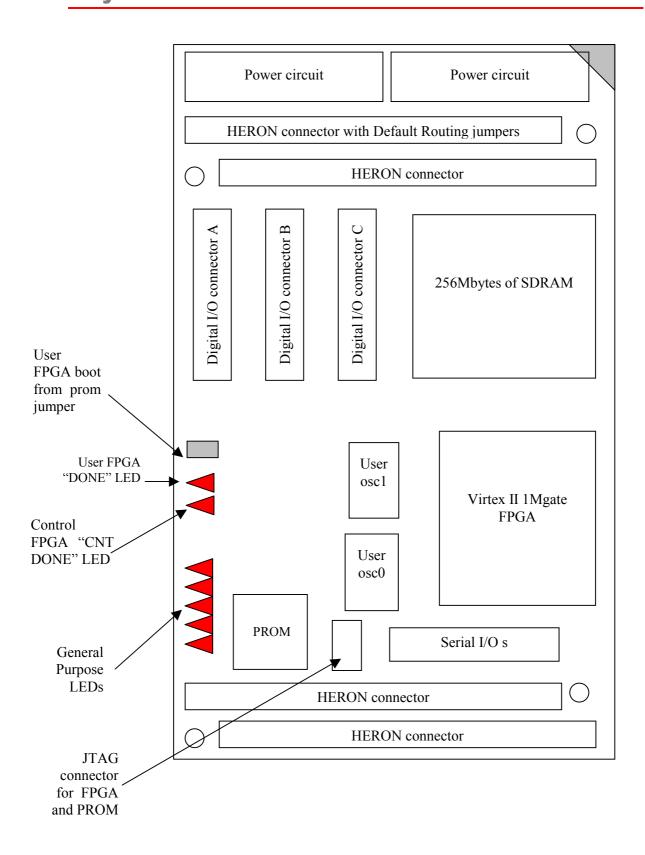

## **Physical Location of Items on the HERON-FPGA5**

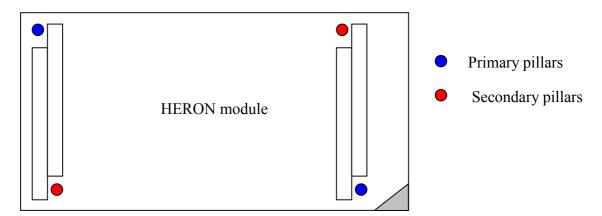

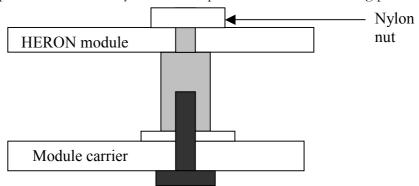

The HERON-FPGA5 is a module that plugs into a HERON module carrier.

The HERON-FPGA5 should be fitted to the carrier card along with any other modules that your system has and their retaining nuts fitted (see a later section of this manual for details).

The Default routing jumpers must be set correctly for the system. For most systems the FPGA based modules will not require any default routing jumpers to be fitted. This will allow the FPGA to access whatever FIFO is needs to, and will rely on the FIFO being connected to the right place by the carrier configuration. (See a later section for details on default routing jumpers).

The HERON-FPGA5, following reset, will enter a state where it can be interrogated and programmed using the HERON module's serial bus. It is addressed according to the Carrier number and the slot number of the HERON slot that it is fitted to.

The FPGA configuration data will have been generated using the Xilinx development tools. HUNT ENGINEERING provide examples for the HERON-FPGA modules in the correct format for use with the Xilinx ISE software. HUNT ENGINEERING also provides software for the Host PC that will allow the output files from the Foundation software to be loaded onto a HERON-FPGA module.

Follow the "Starting your FPGA development" tutorial from the HUNT ENGINEERING CD, and then the general FPGA examples found in the same place on the CD.

It could be possible to use the HERON-FPGA5 as an I/O or memory module using one of the example bit streams. In this case it is not necessary to be concerned how to program the FPGA – simply load the example bit stream and use it.

#### Standard Intellectual Property (IP)

HUNT ENGINEERING provides examples for the HERON-FPGA5 that perform different functions. It is possible to use these standard configurations directly if they fit your needs.

It could be possible to request a new standard example from HUNT ENGINEERING, which could avoid the need to purchase and learn how to use the FPGA development tools. Depending on the complexity of your request HUNT ENGINEERING may choose not to offer it, or to charge for it.

New IP for the HERON-FPGA5 will be posted on the HUNT ENGINEERING web site in the user area whenever it becomes available. HERON-FPGA5 users can then take advantage of that IP free of charge.

This section describes the features of the HERON-FPGA5 and why they are provided.

#### Serial Configuration of the User FPGA

The HERON-FPGA5 usually has the configuration of the user FPGA downloaded using the HERON module's serial configuration bus. This allows the use of "standard" configurations as supplied on the HUNT ENGINEERING CD, or of user defined configurations without the need to return the module to the factory.

It is imagined that as the "standard" set of functions grows, that they be made available to users of HERON-FPGA modules via the HUNT ENGINEERING web site or CD update requests. Also HUNT ENGINEERING will have the possibility to provide semi-custom configurations for a charge via email.

#### **USER FPGA boot ROM**

As an alternative to the serial configuration download, it is possible to configure the FPGA from a Flash based configuration PROM However, if a system is being deployed with a host machine such as a PC, it might be preferable to continue to use the serial configuration method, as this will make in field upgrades and bug fixes simpler to deploy.

The PROM fitted to the FPGA5 is Flash based, and can be programmed (and reprogrammed) using a Xilinx JTAG cable (such as Xilinx Parallel cable 3 or 4). An option in the JTAG download software can cause the FPGA to be configured on completion of the PROM being programmed.

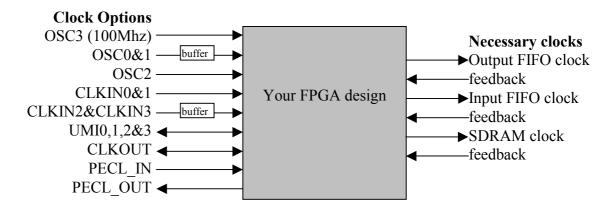

#### Clocking of the FPGA

The Xilinx FPGA used on the HERON-FPGA5 does not have a single clock input, but rather it can use any one of its pins to provide a clock input. This means you can have many sources of clocks, each of which can be used inside your FPGA design. You can even divide these clocks using flip flops, or even multiply using digital clock manager components.

The simplest way to manage your FPGA design is to use just one clock throughout your design. However the FPGA must drive both of the HERON FIFO clocks, at a frequency that is suitable for your module carrier (see the documentation for your module carrier for details of its restrictions). The FPGA must also drive the SDRAM clock, at a frequency suitable for the SDRAM (133MHz). The FPGA may also need to use clocks for the digital I/Os. The frequency for these might be limited by the equipment that it is connected to, or by the needs of your signal processing. The needs for these clocks can only be determined by looking carefully at the needs of your system.

If these clocks cannot be the same, then the next best situation is to have one clock derived from the other. In that way the relationship between the clock edges will be known.

The most difficult case for your FPGA design is to have many clocks from different sources that are all used in the same design. Then you must carefully manage signals that cross from one clock "domain" to another. This can be handled by FIFOS, or by multiple registering to prevent metastability problems. Refer to texts on digital design to understand these issues.

The HERON-FPGA5 provides a highly flexible set of choices for the clocking of the FPGA.

The HERON-FPGA5 has two sockets for user oscillators. It has a further 2 locations for surface mount oscillators to be fitted for designs that require all 4 user oscillators to be used.

Default shipping state is to have a 100Mhz oscillator fitted to one of the surface mount sites – driving 100Mhz on UserOsc3. This is a standard commercial oscillator module that is +100ppm accuracy. If you require higher accuracy clocks then you should use one of the other clock sources.

There is a SERIAL I/Os connector which provides a dedicated PECL input and PECL output. These PECL differential signal pairs can be used to create either a PECL input clock or PECL output clock from the FPGA. Also the UMI pins on the module connector could be used as a clock input, if another module in the system is programmed to drive that clock onto the UMI connection.

#### **HERON FIFOS**

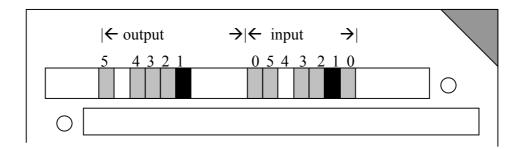

The HERON module can access up to 6 input FIFOs and up to another 6 output FIFOs. Actually it is most likely that a carrier board will not implement all 12 FIFO interfaces. Each FIFO interface is the same as the others, using common clocks and data busses.

The input and output interfaces are separate though, allowing data to be read and written at the same time by a module like the HERON-FPGA5.

While it is possible to read one FIFO and write another FIFO at the same time, the use of shared pins means no more than one can be written or read at the same time.

For each interface (input or output) there is a FIFO clock that must be a constant frequency, and running constantly. There may be some minimum and maximum frequency requirements for a particular Module Carrier card that the designer of the FPGA contents must be sure to comply with. This is because the FIFO clocks are generated by the FPGA, probably based on one of the clock inputs to the part.

Each FIFO interface has a separate "enable" signal that is used to indicate which FIFO is accessed using the clock edge.

#### Input FIFOs

The input FIFOs use a common data bus that is driven onto the HERON module. It is important to ensure that no more than one of the FIFOs are read at the same time, but more importantly that no more than one has its output enable selected.

By properly asserting the "read enable" and "output enable" signals relative to the clock the FPGA can access the FIFO of its choice at a rate up to one 32 bit word per clock cycle.

For the timing of those signals refer to the HERON module specification.

Each input FIFO interface provides Flags that indicate the state of the FIFO. An empty flag shows that there is no data to be read, an almost empty flag shows that there are at least 4 words left. While the almost flag is not asserted accesses can be made on every clock, but after it is asserted, it is better to make one access only, then check the empty flag on the next clock, before deciding if another access is possible.

#### **Output FIFOs**

The output FIFOs use a common data bus that is driven by the HERON module. It is important to ensure that no more than one of the FIFOs is written at the same time – unless that is required by your system.

By properly asserting the "write enable" signals relative to the clock, the user FPGA can access the FIFO of its choice at a rate up to one 32-bit word per clock cycle.

For the timing of those signals refer to the HERON module specification.

Each output FIFO interface provides Flags that indicate the state of the FIFO. A full flag shows that there is no room left to write, an almost full flag shows that there are at least 4 words of space left. While the almost flag is not asserted accesses can be made on every clock, but after it is asserted, it is better to make one access only, then check the full flag on the next clock, before deciding if another access is possible.

#### FIFO clocks

The FIFO clocks are provided by the user FPGA, but are buffered externally using an LVT245 buffer that is able to provide the drive current required on these signals. To enable circuitry internal to the FPGA to be designed to use the actual clock that is applied to the FIFO, the buffered FIFO clock signals are connected to the remaining GCLK inputs. This allows DLLs to be used to provide a clock internal to the FPGA that has the same phase as that applied to the FIFOs on the carrier board.

#### **SDRAM**

The HERON-FPGA5 provides 256Mbytes of SDRAM directly connected to the I/O pins of the Virtex-II FPGA. The SDRAM is organised as a 32-bit wide memory bank of 64M locations.

In order to use the SDRAM correctly, an appropriate SDRAM controller function is required inside the FPGA. This controller must correctly initialise the SDRAM, and provide a constant refresh mechanism.

An appropriate SDRAM controller is provided in the VHDL support from HUNT ENGINEERING. This SDRAM controller can be found in the Hardware Interface Layer and must be used by all designs wishing to use the SDRAM.

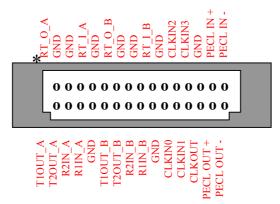

#### Digital I/O

The HERON-FPGA5 connects 45 of the FPGAs I/O pins to connectors. This allows them to be configured as digital Inputs and Outputs as chosen by the user's FPGA program.

For the HERON-FPGA5, Vcco is always connected to 3.3V. Therefore, all FPGA I/O pins used with the Digital I/O connectors must be selected to use an IO standard that is compatible with a 3.3V Vcco.

#### **Module and Carrier ID**

The HERON specification assigns pins on the HERON module that give a HERON module access to the carrier ID of the carrier that it is plugged into, and a unique HERON

slot identifier.

These IDs are used by the configuration FPGA so that the module is addressed on Heron Serial Bus (HSB) using this information. These signals are also connected to the User FPGA so a user program can use them if required.

#### **General Purpose LEDs**

There are some LEDs on the HERON-FPGA5 that are connected via a buffer to some of the FPGA I/O pins. There are five such LEDs, which can be used by the FPGA program to indicate various states of operation.

#### **Done LEDs**

There are two Done LEDs, labelled "DONE" and "CNT DONE". They are illuminated if the relevant FPGA is not configured.

LED "DONE" is connected to the user Virtex-II FPGA.

LED "CNT DONE" is connected to the Control FPGA.

This means that the "CNT DONE" should flash at power on, and then go out showing that the control FPGA is ready to accept a configuration stream for the User FPGA.

After downloading a bitstream to the user User FPGA LED "DONE" should also go out.

#### **Serial Ports**

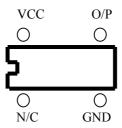

There is a connector on the HERON-FPGA5 that provides the opportunity to use a variety of serial port configurations. There are two MAX3160 "protocol converter" chips provided external to the FPGA, each of which can provide: -

| 1 channel 4 wire RS232     | With RTS and CTS           |

|----------------------------|----------------------------|

| 2 channels of 2 wire RS232 | Without RTS and CTS        |

| 1 channel of 4 wire RS485  | One pair in each direction |

| 2 channels of 2 wire RS485 | Two bi-directional pairs   |

The components are purely voltage level converters, and any UART logic must be implemented in the FPGA.

In addition there is a PECL differential input pair and PECL differential output pair provided on the SERIAL IOs connector. These signal pairs include the correct resistor termination schemes for implementing PECL inputs and outputs with the Virtex-II FPGA.

## **Getting Started on your FPGA Design**

HUNT ENGINEERING provide a comprehensive VHDL support package for the HERON-FPGA5.

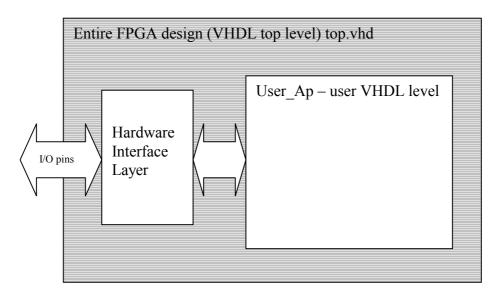

This package consists of a VHDL "top level", with corresponding user constraints file, VHDL sources and simulation files for the Hardware Interface Layer, and User VHDL files as part of the examples.

The Hardware Interface Layer correctly interfaces with the Module hardware, while the top level (top.vhd) defines all inputs and outputs from the FPGA on your module. Users should not edit these files unless a special digital I/O format is required – see the later section "Digital I/O from the FPGA".

The file user\_ap.vhd is where you will make your design for the FPGA, using the simplified interfaces provided by the Hardware Interface Layer.

Organisation of VHDL support for FPGA modules

After synthesising your design, you will use the Place and Route tools from Xilinx (either as part of your ISE package, or from the Xilinx Alliance tools). These tools will use the User Constraints File (.ucf) to correctly define the correct pins and timing parameters. You will need to minimally edit this file to have the timing constraints that you need, but the file provided means you do not need to enter the pin constraints at all.

It is expected that every user will start by following the Getting Started example, Example1, which is supplied on the HUNT ENGINEERING CD. By working through the Getting Started example you will be able to see how the User FPGA is configured, how a simple example can be built, and a new bitstream generated.

In this way, you can use Example1 to check your understanding of how the module works, and you can also use the example as a sanity check that your hardware is functioning correctly.

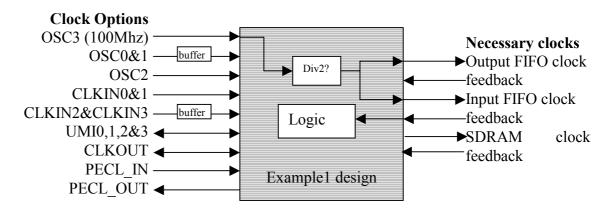

#### **Working through Example 1**

All HERON modules that have FPGAs have an "Example1" provided for them. It is a simple example that connects data from the input FIFO interface to the output FIFO interface, and also exercises the HSB interface.

This example is fully described in the "Starting your FPGA development" tutorial on the HUNT ENGINEERING CD.

The tutorial works through running the example and then modifying and re-building it. The tutorial assumes that you are using the latest version of the ISE Foundation tool-set from Xilinx. If you are using a different version of ISE Foundation, you will simply need to convert the project as described in the application note provided by HUNT ENGINEERING titled 'Using Different Versions of ISE'. There is also an application note on the HUNT ENGINEERING CD that describes using design flows that are different from ISE, titled 'Using VHDL tools other than ISE'.

The example is quite simple but demonstrates the use of the interfaces found in the Hardware Interface Layer supplied with the module. The example is supplied in two ways. Firstly, there is a ready-to-load bitstream, supplied in the Hunt Compressed Bitstream file format, or '.hcb' format. This is the file format used by the HUNT ENGINEERING configuration tool. Secondly, there is an example1 project supplied for ISE, enabling the design to be rebuilt and a new bitstream downloaded.

The bitstream file is provided to allow you to load the example1 onto the hardware without having to re-build it. This is a useful confidence check to see if any problems you are experiencing are due to changes you have made, or the way you have built the design. If the bitstream from the CD fails to behave then the problem is more fundamental.

To make things easier, we have created the proper ISE project files for the examples.

Using these projects will allow you to run the complete design flow, from RTL-VHDL source files to the proper bitstream, ready to download on your Heron FPGA board.

No special skills are required to do this.

However, if you want to write your own code and start designing your own application, you must make sure that you have acquired the proper level of expertise in:

- \* VHDL language,

- \* Digital Design

- \* Xilinx FPGAs

- \* ISE environment and design flow

Proper training courses exist which can help you acquire quickly the required skills and techniques. Search locally for courses in your local language.

#### **Preparing ISE**

Before beginning work with Example1 you will need to make sure ISE is properly installed. In addition, you should ensure that you have downloaded the latest service pack from the Xilinx website for the version of ISE you are using.

#### Copying the examples from the HUNT ENGINEERING CD

On the HUNT ENGINEERING CD, under the directory "fpga" you can find directories for each module type. In the case of the HERON-FPGA5 the correct directory is "fpga5v1".

There are two ways that you can copy the files from the CD.

- 1) The directory tree with the VHDL sources, bit-streams etc can be copied directly from the CD to the directory of your choice. In this case there is no need to copy the .zip file, but the files will be copied to your hard drive with the same read only attribute that they have on the CD. In this case all files in the example directories need to be changed to have read/write permissions ('Example1', camera examples and SDRAM example directories). It is a good idea to leave the permissions of the 'Common' directory set to read only to prevent the accidental modification of these files.

- 2) To make the process more convenient we have provided the zip file, which is a zipped image of the same tree you can see on the CD. If you "unzip" this archive to a directory of your choice, you will have the file permissions already set correctly.

#### **Opening the Example 1 Project**

Let us start with Example1. In the tree that you have just copied from the CD, open the Example1 sub-directory. You should see some further sub-directories there:

- \* ISE holds the ISE project files.

- \* Src holds the application-specific Source files.

- \* Sim holds the simulation scripts for ModelSim.

- \* Leo\_Syn holds the synthesis scripts for Leonardo Spectrum and Synplify users. You may ignore this directory in this chapter.

Open the Xilinx ISE Project Navigator. If a project pops up (from a previous run), then close it. Use File  $\rightarrow$  Open project.

Select Example1\ISE\XXXXX.ise and click on the "Open" button.

After some internal processing, the "Sources window" of the Project Navigator will display the internal hierarchy of the Example1 project.

If you are encountering errors at this stage, you should verify that:

The example files have been correctly copied onto your hard disk, and especially the \Common and Example1\Src directories.

The correct version of ISE has been successfully installed. Be sure to have installed XST VHDL synthesis and the support for the Virtex2 family.

#### The Project's functional parameters

Double click on "user\_ap1" in the Sources window. This opens the VHDL colour-coded text editor so that you can see the part of the project where you can enter your own design.

The first code that you will see at the beginning of this file is a VHDL Package named "config" which is used to configure the design files according to the application's requirements. See the next section of this manual for a description of these items.

Below the package section, you will see the User\_Ap1's VHDL code.

This is where you will insert your own code when you make your own design.

We provide a system which is built in such a way that the user should not need to edit any other file than User\_Ap (and the entities that this module instantiates).

In particular, the user should NOT modify the HE\_\* files, even when creating new designs for the FPGA.

#### **Setting up the Configuration Package**

At the top of the file USER\_APx.VHD (where x indicates the example number) there are settings that you can change to affect your design (in this case the example). The idea is that settings that are often changed are found here.

#### 1. Divide External Clock by 2

The example uses the 100Mhz oscillator that is fitted to Osc3 of the module. It generates the FIFO clock either directly from this 100Mhz, or divides it by 2 to generate a 50Mhz FIFO clock. Unfortunately the HEPC8 module carrier cannot support a clock as high as 100Mhz, and the HEPC9 carrier cannot support a clock as low as 50Mhz.

Set this parameter to "True" if you want to divide the external clock by two and use this as your main Clock.

If you are using an HEPC8 carrier board, set DIV2\_FCLK to "True".

If you are using an HEPC9 carrier board, set DIV2\_FCLK to "False".

#### 2. FIFO Clocks

You must decide whether you will have a single common clock for driving the input and output FIFOs. Normally a design is simpler if the same clock is used for input and output FIFOs, but the module design allows you to use different frequencies or phases if that is more convenient for the design of your system. Whether you use a common clock or separate clocks will affect your design, but it also affects the use of clocks in the Hardware Interface Layer.

Set FCLK\_G\_DOMAIN to True if you have the same clock driving both FIFOs. This is the default option for the Examples. If you are unsure, select this choice.

Then, you must know whether your clocks are running slower than 60 MHz or not. This is the frequency that *you* connect to the SRC\_FCLK\_G in your design.

Set HIGH\_FCLK\_G to True if your global clock is running at 60 MHz or above. In this case an HF DLL will be used in the FIFO clocks to ensure the proper timing.

Set HIGH\_FCLK\_G to False otherwise. In this case the HF DLL does not work, and an LF DLL is necessary.

Set FCLK\_G\_DOMAIN to False is you have a different clock driving each Fifo. This option should be reserved to advanced users familiar with the management of multiple clock domains systems.

Then, you must know whether each of your clocks are running slower than 60 MHz or not. These are the frequencies that *you* connect to the SRC\_FCLK\_RD and SRC\_FCLK\_WR in your user\_ap.

Set HIGH\_FCLK\_RD to True if your Input Fifo clock is running at 60 MHz or above, so that the HF DLL will be used for the input FIFO clock.

Set HIGH\_FCLK\_RD to False otherwise, so a LF DLL will be used for the input FIFO clock.

Set HIGH\_FCLK\_WR to True if your Output Fifo clock is running at 60 MHz or above, so that the HF DLL will be used for the output FIFO clock.

Set HIGH\_FCLK\_WR to False otherwise, so that a LF DLL will be used for the output FIFO clock.

The Table below summarises the available choices:

| FCLK_G_DOMAIN | HIGH_FCLK_G  | HIGH_FCLK_RD | HIGH_FCLK_WR |

|---------------|--------------|--------------|--------------|

| True          | True / False | n.a.         | n.a.         |

| False         | n.a.         | True / False | True / False |

In the case of example1, the correct choices are:

#### For the HEPC8

| DIV2_FCLK | FCLK_G_DOMAIN | HIGH_FCLK_G | HIGH_FCLK_RD | HIGH_FCLK_WR |

|-----------|---------------|-------------|--------------|--------------|

| True      | True          | False       | n.a.         | n.a.         |

#### For the HEPC9

| DIV2_FCLK | FCLK_G_DOMAIN | HIGH_FCLK_G | HIGH_FCLK_RD | HIGH_FCLK_WR |

|-----------|---------------|-------------|--------------|--------------|

| False     | True          | True        | n.a.         | n.a.         |

#### **User Timing Constraints**

As with all FPGA designs it is necessary to apply some timing constraints to the design to ensure that the tools generate a design that will operate at the frequency that you require. Example 1 has these defined in the '.ucf' file.

Although you can use the configuration package to set the frequency of the FIFO clocks to be 50Mhz, you can still use the stricter timing constraints needed when those clocks run at 100Mhz. So in the case of example1 you do not need to change any of the timing constraints. When you make changes to the design however you may find that you introduce more clock nets that need to be added to the ucf file. In some cases you may find that the tools are unable to achieve your desired clock frequency and then (if you are using an HEPC8) you should change the constraints to reflect you true needs.

For more details on Timing Constraints please refer to the Xilinx tools documentation.

#### **Creating the Bitstream for Example1**

Once the project has been opened as described above:

- 1. In the "Sources in project" window (Project Navigator), highlight (*single*-click on) the entity 'top' ("..\..\Common\top.vhd"). This is extremely important! Otherwise, nothing will work!

- 2. Double-click on the "Generate Programming File" item located in the "Processes for Current Source". This will trigger the following activity:

Complete synthesis, using all of the project's source files. Since warnings are generated at this stage, you should see a yellow exclamation mark appear besides the "Synthesize" item in the Processes window.

Complete Implementation:

Translation

Mapping

Placing

Routing

3. Creation of the bitstream. Note that this stage runs a DRC check, which can potentially detect anomalies created by the Place and route phase.

When the processing ends, the proper bitstream file, with extension ".rbt" can be found in the project directory. This file MUST be called top.rbt. If it is not then you have synthesised a small part of your design because you did not properly highlight top.vhd in step1.

4. In the "Pad Report" verify a few pins from the busses, like: LED(0) = M1, LED(1) = M2, LED(2) = M3, LED(3) = M4, etc. To do this you need to open "implement design" in the processes window, then open "Place and Route".

Then double click on the pad report to open it. If you see different assignments, STOP HERE, and verify the UCF file selected for the project.

You can download this file on your FPGA board and see how it works. See a later section of this manual.

Note that the user\_ap level includes a very large counter that divides the main system clock and drives the LED #4. It is then obvious to see if the part has been properly programmed and downloaded: the LED should flash. The hardware will probably require a reset after configuration before the LED starts to flash.

If the LED does not flash, we recommend that you shut down the PC or reprogram the device using a "safe" bitstream. Otherwise, some electrical conflicts may happen (see below).

Possible causes for the device failure to operate are:

1. Wrong (or no) UCF file. This happens (for example) if you select the XST-version of the UCF with a Leonardo Spectrum (or Synplify) synthesis. The pin assignment for all the vectors (busses) will be ignored, and these pins will be distributed in a quasi-random fashion!

- 2. Wrong parameters in the CONFIG package.

- 3. Design Error.

If nothing seems obvious, rerun the confidence tests, then return to the original example 1.

#### Simulating the Complete Design

To generate the bitstream as above, you did not need to do any simulation. However, if you start modifying the provided examples and add your own code, verification can soon became an important issue.

If you need to simulate your design, you will need to install a VHDL simulator such as ModelSim (available in Xilinx Edition, Personal Edition, or Special Edition).

The example projects provided on the HUNT ENGINEERING CD include simulation files that provide a starting point for simulating your own design. If you wish to work through the simulation examples provide, please read the document 'Simulating HERON FPGA Designs'.

## **Making your own FPGA Design**

The actual contents of the User FPGA on the HERON-FPGA5 are generated by the user. While making this development requires some knowledge of Digital Design techniques, it is made quite simple by the development environment that you use.

We recommend the Foundation ISE series software available from Xilinx, because that is what we use at HUNT ENGINEERING, and any examples and libraries we provide are tested in that environment. However there are other tools available from third parties that can also be used. The use of VHDL sources for our Hardware Interface Layer and examples means that virtually any FPGA design tool could be used. Any development tool will eventually use the Xilinx Place and Route tool, where the user constraints file that we supply will ensure that the design is correctly routed for the module. There are application notes on the HUNT ENGINEERING CD that describe how other tools might be used.

The best way to learn how to use your development tools is to follow any tutorials provided with them, or to take up a training course run by their vendors.

ALL NEW PROJECTS SHOULD START FROM ONE OF THE PROVIDED EXAMPLES – that way all of the correct settings are made, and files included. Your design should take place entirely within the User-Ap level, except in the case of needing to change the I/O formats of the Digital I/Os in which case it is necessary to minimally edit the top.vhd file – see a later section in this manual for details.

It is assumed that you are able to use your tools and follow the simplest of Digital Design techniques. HUNT ENGINEERING cannot support you in these things, but are happy to field questions specific to the hardware such as "how could I trigger my A/D from a DSP timer?" or "How can I use the FIFO interface component to do….?".

#### User\_Ap Interface

This section describes the Interface between the User\_Ap central module (or *entity* using VHDL terminology) and the external Interface hardware. This is the part where you connect your FPGA design to the resources of the module.

In other words:

- 1. The Clocks system

- 2. How your application can communicate with the external world: Digital I/Os, HSB interface, FIFOs and SDRAM.

You need to understand this interface in order to properly connect your processing logic.

The complete FPGA project consists of a Top level in which many sub-modules (entities) are placed (instantiated) and interconnected. One of these modules is User\_AP: your module.

The top-level and the other modules make the system work, but you do not have to understand nor modify them in any way.

Let us see all of the Inputs/Outputs (*Ports*) of your User\_Ap module:

Note that the names used for these ports are effectively "reserved" even if the user does not connect to that signal. This means the user must be careful not to re-use the same name for

a signal that should not connect to these ports.

| Port          | Direction in User_Ap | Description                                                                   |

|---------------|----------------------|-------------------------------------------------------------------------------|

| GENERAL       |                      |                                                                               |

| RESET         | In                   | Asynchronous module reset (active high)                                       |

| CONFIG        | In                   | System config signal (active low)                                             |

| ADDR_FLAGSEL  | In                   | Module input to select the mode of some module pins – see HERON specification |

| BOOTEN        | Out                  | Module output not normally used                                               |

| UMI_EN[0:3]   | Out                  | Uncommitted Module Interconnect enables, FPGA output driven when low          |

| UMI_IN[0:3]   | In                   | Uncommitted Module Interconnects in                                           |

| UMI_OUT[0:3]  | Out                  | Uncommitted Module Interconnects out                                          |

| MID[0:3]      | In                   | Module ID of this module slot                                                 |

| CID[0:3]      | In                   | Carrier ID of this carrier                                                    |

| UDPRES        | Out                  | Optional reset to system. Drive to '1' if not used.                           |

| LED[0:4]      | Out                  | 5 x LEDs, can be used for any purpose                                         |

| CLOCK SOURCES |                      |                                                                               |

| OSC0          | In                   | External Clock from OSC0 oscillator                                           |

| OSC1          | In                   | External Clock from OSC1 oscillator                                           |

| OSC2          | In                   | External Clock from OSC2 oscillator                                           |

| OSC3          | In                   | External Clock from OSC3 oscillator                                           |

| CLKIN0        | In                   | Unbuffered External Clock from SERIAL I/Os connector                          |

| CLKIN1        | In                   | Unbuffered External Clock from SERIAL I/Os connector                          |

| CLKI2         | In                   | Buffered External Clock from SERIAL I/Os connector                            |

| CLKI3         | In                   | Buffered External Clock from SERIAL I/Os connector                            |

| CLOCK OUTPUTS |                      |                                                                               |

| CLKOUT        | Out                  | Unbuffered External Clock to SERIAL I/Os connector                            |

| PECL I/Os     |                      |                                                                               |

| PECL_IN       | In                   | PECL input from SERIAL I/Os connector                                         |

| PECL_OUT             | Out | PECL output to SERIAL I/Os connector                                          |

|----------------------|-----|-------------------------------------------------------------------------------|

| SERIAL I/OS          |     |                                                                               |

| T1IN_A               | Out | Data driven to RS232/485 chip                                                 |

| T2IN_A               | Out | Data driven to RS232/485 chip                                                 |

| R1OUT_A              | In  | Data input from RS232/485 chip                                                |

| R2OUT_A              | In  | Data input from RS232/485 chip                                                |

| RS485_232_A          | Out | Control signal driven to RS232/485 chip                                       |

| HDPLX_A              | Out | Control signal driven to RS232/485 chip                                       |

| FAST_A               | Out | Control signal driven to RS232/485 chip                                       |

| T1IN_B               | Out | Data driven to RS232/485 chip                                                 |

| T2IN_B               | Out | Data driven to RS232/485 chip                                                 |

| R1OUT_B              | In  | Data input from RS232/485 chip                                                |

| R2OUT_B              | In  | Data input from RS232/485 chip                                                |

| RS485_232_B          | Out | Control signal driven to RS232/485 chip                                       |

| HDPLX_B              | Out | Control signal driven to RS232/485 chip                                       |

| FAST_B               | Out | Control signal driven to RS232/485 chip                                       |

| FIFO CLOCK           |     |                                                                               |

| INTERFACE            |     |                                                                               |

| FCLK_RD              | In  | Read FIFO Clock to be used in this module (only when FCLK_G_DOMAIN = FALSE)   |

| SRC_FCLK_RD          | Out | Input FIFO Clock source for the top level (only when FCLK_G_DOMAIN = FALSE)   |

| FCLK_WR              | In  | Output FIFO Clock to be used in this module (only when FCLK_G_DOMAIN = FALSE) |

| SRC_FCLK_WR          | Out | Output FIFO clock source for the top level (only when FCLK_G_DOMAIN = FALSE)  |

| FCLK_G               | In  | Common FIFO clock to be used in this module (only when FCLK_G_DOMAIN = TRUE)  |

| SRC_FCLK_G           | Out | Common FIFO clock source for the top level (only when FCLK_G_DOMAIN = TRUE)   |

| INPUT FIFOs          |     |                                                                               |

| INFIFO_READ_REQ[5:0] | Out | Input FIFO Read Request                                                       |

| INFIFO_DVALID[5:0]   | In  | Input FIFO Data Valid                                                         |

| INFIFO_SINGLE[5:0]   | In  | Input FIFO Single Word Available                                              |

| INFIFO_BURST[5:0]    | In  | Input FIFO Burst Possible                                                     |

| INFIFO0_D [31:0]   | In  | Input FIFO 0 Data                                                                      |

|--------------------|-----|----------------------------------------------------------------------------------------|

| INFIFO1_D [31:0]   | In  | Input FIFO 1 Data                                                                      |

| INFIFO2_D [31:0]   | In  | Input FIFO 2 Data                                                                      |

| INFIFO3_D [31:0]   | In  | Input FIFO 3 Data                                                                      |

| INFIFO4_D [31:0]   | In  | Input FIFO 4 Data                                                                      |

| INFIFO5_D [31:0]   | In  | Input FIFO 5 Data                                                                      |

| OUTPUT FIFOs       |     |                                                                                        |

| OUTFIFO_READY[5:0] | In  | Output FIFO Ready for Data                                                             |

| OUTFIFO_WRITE[5:0] | Out | Output FIFO Write Control                                                              |

| OUTFIFO_D [31:0]   | Out | Data written into Output FIFO                                                          |

| HE_USER I/F        |     |                                                                                        |

| MSG_CLK            | Out | Clock to HE-USER interface logic.                                                      |

| MSG _DIN [7:0]     | In  | Data received from HSB                                                                 |

| MSG _ADDR [7:0]    | In  | "address" received from the HSB                                                        |

| MSG _WEN           | In  | Write access from the HSB                                                              |

| MSG _REN           | In  | Read access from the HSB                                                               |

| MSG _DONE          | In  | Message was successfully transmitted (used when initiating HSB messages)               |

| MSG _COUNT         | In  | Counter enable when initiating HSB messages                                            |

| MSG _CLEAR         | In  | Asynchronous clear for address counter when initiating HSB messages                    |

| MSG _READY         | Out | to acknowledge an access from the HSB                                                  |

| MSG _SEND          | Out | Message send command (used when initiating HSB messages)                               |

| MSG _CE            | Out | to control speed operation                                                             |

| MSG _DOUT [7:0]    | Out | Data to be sent to HSB                                                                 |

| MSG _SEND_ID       | Out | Indicates when a byte should be replaced by Own ID (used when initiating HSB messages) |

| MSG _LAST_BYTE     | Out | To indicate when the last byte to be sent is presented when initiating HSB messages    |

| DIGITAL I/O        |     |                                                                                        |

| CONN_A_EN[0:7]     | Out | Digital I/O enables for connector A, FPGA output pin driven when low                   |

| CONN_A_IN[0:7]     | In  | Digital I/O in for connector A                                                         |

| CONN_A_OUT[0:7]    | Out | Digital I/O out for connector A                                                        |

| CONN_B_EN[0:7]     | Out | Digital I/O enables for connector B, FPGA                                              |

|                     |     | output pin driven when low                                           |

|---------------------|-----|----------------------------------------------------------------------|

| CONN_B_IN[0:7]      | In  | Digital I/O in for connector B                                       |

| CONN_B_OUT[0:7]     | Out | Digital I/O out for connector B                                      |

| CONN_C_EN[0:7]      | Out | Digital I/O enables for connector C, FPGA output pin driven when low |

| CONN_C_IN[0:7]      | In  | Digital I/O in for connector C                                       |

| CONN_C_OUT[0:7]     | Out | Digital I/O out for connector C                                      |

| SDRAM I/F           |     |                                                                      |

| SDRAM_WR_DATA[31:0] | Out | SDRAM Write Port Data                                                |

| SDRAM_WR_ADDR[25:0] | Out | SDRAM Write Port Address                                             |

| SDRAM_WR_AEN        | Out | SDRAM Write Port Address enable                                      |

| SDRAM_WR_READY      | Out | SDRAM Write Port data-ready                                          |

| SDRAM_WR_BURST      | Out | SDRAM Write Port burst-ready                                         |

| SDRAM_WR_DONE       | In  | SDRAM Write Port write access completed                              |

| SDRAM_RD_DATA[31:0] | In  | SDRAM Read Port Data                                                 |

| SDRAM_RD_ADDR[25:0] | Out | SDRAM Read Port Address                                              |

| SDRAM_RD_AEN        | Out | SDRAM Read Port Address enable                                       |

| SDRAM_RD_READY      | Out | SDRAM Read Port data-ready                                           |

| SDRAM_RD_BURST      | Out | SDRAM Read Port burst-ready                                          |

| SDRAM_RD_DONE       | In  | SDRAM Read Port read access completed                                |

| SDRAM_RD_DVAL       | In  | SDRAM Read Port data valid                                           |

#### **Hardware Interface Layer**

All of the signals listed above are connected between the 'User\_Ap' interface and the pins of the FPGA via the 'Hardware Interface Layer'. The Hardware Interface Layer includes logic that correctly interfaces many different functional parts of the FPGA, from HERON-FIFO interfaces, SDRAM interface, to clock inputs and outputs, to digital I/O and serial I/O.

For a complete description of the Hardware Interface Layer (HIL), please read the document 'Using the Hardware Interface Layer in your FPGA Design'.

Starting from Serial number J013 the SDRAM manufacturer introduced a new SDRAM part that requires different bank management. This is taken care of inside the Hardware Interface Layer supplied, but care must be taken to use the correct HIL with the correct modules. Modules J001 to J012 inclusive are Version 1 and should use the FPGA5V1 H.I.L., modules from J013 onwards are version 2 and should use the FPGA5V2 H.I.L. Users FPGA code is unchanged by this version change.

#### Important!

There are many signals that are connected between the FPGA on the HERON-FPGA5 and the HERON module connectors. Most of these signals will only be used by advanced users of the HERON-FPGA5. The FPGA pinning of these signals is defined in the UCF file, and the top.vhd has these signals commented out. Users that want to use these signals will need to uncomment them in the top.vhd and add the correct ports to the user\_ap.vhd.

The FPGA sets any I/O pins of the device that are not listed in the design to have a 50-150K pull down. Most of the HERON module signals are pulled to their inactive state by 10K resistors so this 50K will have no effect. However the UDPRES signal does not, and setting this signal low will cause your whole board to be reset. Thus it is important that the UDPRES pin is driven high by the FPGA if it is not being used.

It is also advised to do the same with the LED pins to prevent them becoming illuminated erroneously.

#### **Other Examples**

There are some other examples (source and .rbt files) provided for the HERON-FPGA5 on the HUNT ENGINEERING CD. Follow "Getting Started" and then "Starting with FPGA". Choose "General FPGA Examples" and click on the directory for the fpga5. The examples are in the directories Memory\_Test(ex2), SDRAM\_FIFO(ex3) etc.

These examples have 'pdf' documents that describe their function.

The second example, 'Memory\_Test' is useful for users who wish to validate that the SDRAM memory fitted to their module is good.

The third example, 'SDRAM\_FIFO' is provided for users who need the SDRAM to behave like a big FIFO. In fact, in this example the SDRAM is used to create two independent 128Mbyte FIFOs.

Please note that as with the examples any "user" work should be done in the user\_ap section i.e. do not put your own logic into the hardware interface layer, but simply include them into your own design. This enables your design to be protected from hardware specific details like pin-out, and also allows you to benefit from any new versions that HUNT Engineering might make available without having to re-work your part of the design.

#### How to Make a New Design

For any new design that you make, it is important that you start from the examples provided on the HUNT ENGINEERING CD.

When making a new design for the HERON-FPGA5 by starting from one of the examples you will already have a project that is correctly set up to use the supplied Hardware Interface Layer. The project will already include the correct settings and user constraints.

In fact, in all situations you should start development from one of the examples on the HUNT ENGINEERING CD, even if you intend to develop the FPGA in a way that is completely different to any of the examples.

In the case where you are to make a new design that does not match a standard example,

you should start development from Example1 and add your own logic in place of the existing Example1 VHDL. By doing this, you will automatically inherit the proper ISE settings, user constraints and project structure.

When your are creating a new design from one of the standard CD examples you will need to be sure that the version of ISE design tools you are using matches the version of ISE for which the example projects were created. If you are using a different version of ISE then you must work through the HUNT ENGINEERING application note 'Using Different Versions of ISE'.

In developing new VHDL, there are proper training courses that exist to help you quickly acquire the required skills and techniques. Search locally for suitable training on these subjects. You may also consider sub-contracting part or whole of the new FPGA design.

#### Inserting your own Logic

When making a new design, you will create and insert your own logic inside the USER\_AP module.

From here you can interface to the HERON FIFOs, the SDRAM, the HSB and the general purpose digital I/Os.

When these interfaces are simple, you may code the proper logic directly in the USER\_AP module.

For more complex interfaces, you may code separate entities in separate source files, and instantiate these entities within USER\_AP, as was done in the Examples.

Important: the first thing to edit in the user\_ap.vhd file is the package section where generic parameters are set to match your configuration and your design.

Important: The HE\_USER interface cannot be left entirely unconnected. If you have a design that does not use the features of this interface, you must be certain to connect the following. The Clock of the HE\_USER must be running. The inputs MSG\_SEND, MSG\_SEND\_ID, MSG\_LAST\_BYTE and MSG\_CS must be connected to 0. The MSG\_READY must be connected to '1'.

#### Top-level Fine Tuning (using other special IO pins)

The top level defines all of the I/O pins from the FPGA. Some of them are not used in the examples, but have buffers instantiated in the top.vhd. Some of those pins can have alternative signal formats that require a different Xilinx primitive to be instantiated for the buffers.

Refer to the hardware details section of this manual to learn which pins are suitable for which use.

If the buffers that are already instantiated in top.vhd (usually LVTTL) are suitable for your needs then there is no need to modify top.vhd, you can simply use the signals that are connected as ports to the user\_ap file.

If you need different buffer types then it is necessary to edit top.vhd.

The method to do that is:

Make a copy of the original TOP.vhd file (from /Common) and work on this copy.

Each I/O pin has a buffer type instantiated in top.vhd.

Edit the instantiation to use the proper Xilinx Buffer primitive. You may sometimes have to insert attributes in the UCF file to qualify the IO.

Modify the User\_Ap entity to make these signals visible.

Add the signals in the User\_Ap instantiation port map.

#### **User Timing Constraints**

As with all FPGA designs it is necessary to apply some timing constraints to the design to ensure that the tools generate a design that will operate at the frequency that you require. These will be defined in the .ucf file.

The .ucf file provided as a template has some timing constraints already, but when you make changes to the design you may find that you introduce more clock nets that need to be added to the ucf file.

For more details on Timing Constraints please refer to the Xilinx tools documentation.

#### **Hints for FPGA Designs**

Having said that we cannot support you in making your FPGA design, we always try to make your development easy to get started, so this section outlines some things that you need to think about.

The FPGAs are basically synchronous devices. That is they register data as it passes through the device – making a processing pipeline. It is possible to apply asynchronous logic to signals but the FPGA concept assumes that logic is between registers in the pipeline.

This pipeline gives rise to two things that you need to consider. One is the maximum clock frequency that that pipeline can operate at, and the other is the number of pipeline stages in the design.

As with any component in your FPGA design, components from the HERON-FPGA5 component library operate synchronously. That is, any control or data signal that you connect to the library component must be generated from logic that uses the same clock signal that is connected to the library component. Similarly, logic that is connected to outputs of the library component will need to be clocked by the same clock signal.

For a conventional circuit design, you would normally need to consider the signal delays from the output of one synchronous element to the input of the next element. By adding up a 'clock to output' delay from the output of the first element, adding routing delays and the 'setup to clock' delay for the input of the second element you would have a timing figure to match against the clock period. If the calculated figure is found to be too large, the circuit must be slowed down, or logic must be simplified to reduce the calculated value to one that fits the requirements.

When creating a design using the Xilinx development tools however, you only need to add a timing specification to the clock net that is used to clock both elements. This specification, which may be supplied in units of time or units of frequency will be automatically used by the tool to check that the circuit will run at the specified speed.

This leaves you free to focus on the functionality of the signals, while the Xilinx implementation tools work on achieving your specified time constraints. If at the end of your implementation the tools tell you that your timing constraints have been achieved,

then the combination of all setup, hold and routing delays are such that your design will operate at the frequency you defined.

What this means for your design is that when you place a library component you need to consider whether signals are set high or low correctly on each clock edge (note, all library components are positive/rising edge clocked). What you do not need to worry about is the timing issues of each signal beyond having applied a time constraint on to the clock net that is applied to those components and the connected logic.

#### **Use of Clocks**

Because of the assumption that the design is a pipeline, the development tools will allow you to enter a specification for the clocks used in the design. This allows you to specify the frequency that you need the resulting design to operate at.

Simple designs will use only one clock, and all parts of the design will use that clock. It is usual for every "part" of the design to use the rising edge of this clock. This makes it very simple for the development tools to determine the maximum possible frequency that design could be used at. Adding too much combinatorial logic between pipeline stages will reduce the maximum possible clock rate. This gives rise to a hint – If your design will not run fast enough, add some more pipelining to areas where lots of combinatorial logic is used.

Typically development tools will give a report stating the maximum clock rate that can be used in a particular design, and will probably raise errors if that is slower than the specification that you have provided for the clock used in the design.

More complicated designs would use several clock nets, which may be related in frequency or phase, or may be completely independent. In such a design you must be careful when outputs from logic using one clock are passed to logic using a different clock. It is often useful to add a FIFO, which allows input and output clocks to be completely independent.

#### **Possible Sources of Clocks**

As you can see from the section above, an FPGA design may require one or more clock frequencies to achieve the job it needs to do. How *you* implement *your* design governs the number and frequencies of the clocks you need. The design of the module has been made to give you as much flexibility as possible, but ultimately it is up to you which will be used.

On the HERON-FPGA5 there are four possible Crystal oscillator modules, and four external clocks possible from the CLOCKS connector, as well as differential PECL clock input. Any of these can be used as clocks in the FPGA design, as can clocks provided on any of the other I/Os. One technique for example could be to use one of the UMI pins as a clock input, which can be driven by the timer of a DSP module, or possibly another FPGA module driving a clock onto that UMI. This type of use though is system specific, and we cannot supply a generic example for that. The examples that we provide for the module assume a clock is fitted to the UserOSC0 socket, and use that as the only clock in the design.

#### **Flow Control**

Because the processing speed of the FPGA will almost never be the same as every other component in your system it will be necessary to use some flow control in your design. The most general way to implement this is to use Clock enables to enable the processing only when it is possible for data to flow through the "system". Otherwise some type of data

storage (like FIFOs) must be implemented to ensure that data is never lost or generated erroneously.

When data is read from the HERON Input FIFOs there are FIFO flags to indicate when there is data to be read. Reading from the FIFO when the flags indicate that there is no data to read will result in false data being fed through your system. Thus your design must either a) only assert the read signal when the Empty Flag (EF) is not asserted, or b) use the EF as a clock enable for the logic in the design, thus preventing the invalid data caused by reading an empty FIFO, from being propagated through the design. The actual method used will depend on the needs of the design.

When data is written to the HERON Output FIFOs there are flags to indicate when it is possible to write new data. Writing to the FIFO when the flags indicate there is no room will result in data being lost from your system. Thus your design must not assert the Write enable signal when the Full Flag (FF) is asserted.

#### Pipeline Length or "latency"

The latency of your design will be determined by the length of the pipeline used in your FPGA design. The simplest way to determine this is to "count" the Flip-Flops in your data path, but whichever tools you are using might provide a more elegant way. For example the "Core Generator" will state the pipeline steps used with each core, and will even let you specify a maximum in some cases.

#### I/O from the FPGA

In addition to the FIFO, SDRAM and HSB interfaces of the HERON-FPGA5, there are some General purpose Digital I/O connectors and some options for serial interfaces. The use of these interfaces will be specific to a particular design, so they have not been included in the examples supplied. The pins to use are defined in the top.vhd, and the locations are already defined in the .ucf files. The choice of buffer type and the time specs of those interfaces must be taken care of by the designer.

#### **DSP** with your **FPGA**

The FPGA can be used to perform powerful Digital Signal Processing. It is beyond the scope of this manual and indeed not part of the normal business of HUNT ENGINEERING to teach you how to do this. There is however a simple way to build Signal Processing systems for the Xilinx FPGAs.

Xilinx supply as part of their tool-set something called a "Core Generator". This provides a simple way of generating filters, FFTs and other "standard" signal processing elements, using a simple graphical interface. It results in a "block" that can be included in your design and connected like any other component. Typically it will have a clock input that will be subject to the pipeline speed constraints, and clock enables to allow flow control.

Using the Core Generator you can quickly build up signal processing systems, but for more complex systems you should take a course on Signal Processing theory, and perhaps attend a Xilinx course on DSP using FPGAs.

The software for use with your FPGA will consist of several parts:

#### **FPGA Development tool**

The application contents of the FPGA will be generated using FPGA development tools. Xilinx ISE is the recommended tool, along with ModelSim if you require simulation.

It is possible to use alternative FPGA synthesis tools such as Leonardo Spectrum, or Synplicity, but ultimately the Place and Route stage will be performed by the same tool. Users of ISE have the Place and Route tool included, but users of the other tools require the Xilinx Alliance tool.

The FPGA design can be entered using VHDL.

#### **Design Files for the FPGA**

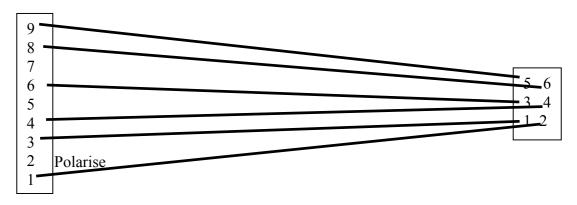

The FPGA design can be downloaded onto the FPGA5 in two ways. Via the Configuration serial bus which requires a \*.rbt file or \*.hcb file, or via the Flash PROM on the JTAG chain which requires a \*.mcs file.

#### **Generating Design Files**

#### Files for HERON Utility (\*.rbt)

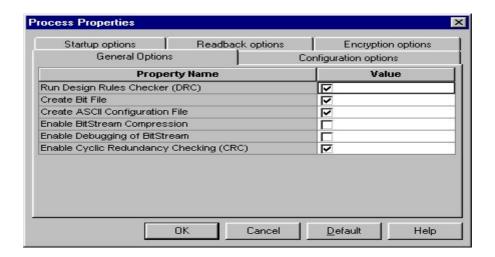

The sections in this document titled "Creating a Project" and "Inserting your own logic" lead up to the generation of a \*.rbt file which can be downloaded via the Configuration serial bus using the HERON Utility. Before generating the \*.rbt file right click on "generate Program File" in the "processes for Current Source" window in ISE, select "Properties" on the menu and then select "General Options". Check that "create ASCII Configuration File "has been selected.

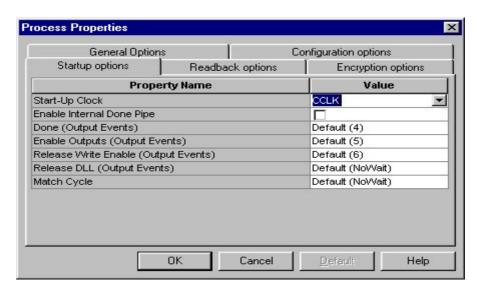

Also from "Process Properties" select the "Start-up Options" and check that CCLK has been selected for the "Start-Up Clock". This is the default used in the example projects provided.

#### Files for PROMs (\*.mcs)

The Flash PROM on the FPGA5 can be programmed, and reprogrammed via the JTAG chain using '\*.mcs' files. These files are generated by the Xilinx "PROM File Formatter" after the '\*.rbt' file has been generated.

Please read the document "Using iMPACT with FPGA modules" for a detailed description of how to create the correct '.mcs' file for your design.

#### **HERON\_FPGA Configuration Tool**

HUNT ENGINEERING provides a tool to allow you to load the FPGAs in your system with .rbt files that you create, or copy from the CD.

For details about using this tool refer to the "Started your FPGA development" tutorial on the HUNT ENGINEERING CD.

The windows tool actually calls a program with command line parameters set according to your choices.

The program is HRN\_FPGA.exe which will have been installed on your DSP machine in the directory %HEAPI\_DIR%\utils.

For help using that program directly type hrm\_fpga -h in a DOS box.

#### **HUNT ENGINEERING HOST-API**