#### **HUNT ENGINEERING**

Chestnut Court, Burton Row, Brent Knoll, Somerset, TA9 4BP, UK

Tel: (+44) (0)1278 760188, Fax: (+44) (0)1278 760199, Email: sales@hunteng.co.uk http://www.hunteng.co.uk http://www.hunt-dsp.com

# HUNT ENGINEERING HECPC19

# 6U CompactPCI, HEART based HERON Module Carrier USER MANUAL

Hardware Rev B Document Rev D M. Siggins 30-6-06 This documentation and the product it is supplied with are Copyright HUNT ENGINEERING 2002. All rights reserved. HUNT ENGINEERING maintains a policy of continual product development and hence reserves the right to change product specification without prior warning.

#### WARRANTIES LIABILITY and INDEMNITIES

HUNT ENGINEERING warrants the hardware to be free from defects in the material and workmanship for 12 months from the date of purchase. Product returned under the terms of the warranty must be returned carriage paid to the main offices of HUNT ENGINEERING situated at BRENT KNOLL Somerset UK, the product will be repaired or replaced at the discretion of HUNT ENGINEERING.

Exclusions - If HUNT ENGINEERING decides that there is any evidence of electrical or mechanical abuse to the hardware, then the customer shall have no recourse to HUNT ENGINEERING or its agents. In such circumstances HUNT ENGINEERING may at its discretion offer to repair the hardware and charge for that repair.

Limitations of Liability - HUNT ENGINEERING makes no warranty as to the fitness of the product for any particular purpose. In no event shall HUNT ENGINEERING'S liability related to the product exceed the purchase fee actually paid by you for the product. Neither HUNT ENGINEERING nor its suppliers shall in any event be liable for any indirect, consequential or financial damages caused by the delivery, use or performance of this product.

Because some states do not allow the exclusion or limitation of incidental or consequential damages or limitation on how long an implied warranty lasts, the above limitations may not apply to you.

#### **TECHNICAL SUPPORT**

Technical support for HUNT ENGINEERING products should first be obtained from the comprehensive Support section <a href="www.hunteng.co.uk/support/support.htm">www.hunteng.co.uk/support/support.htm</a> on the HUNT ENGINEERING web site. This includes FAQs, latest product, software and documentation updates etc. Or contact your local supplier - if you are unsure of details please refer to <a href="www.hunteng.co.uk">www.hunteng.co.uk</a> for the list of current re-sellers.

HUNT ENGINEERING technical support can be contacted by emailing support@hunteng.co.uk, calling the direct support telephone number +44 (0)1278 760775, or by calling the general number +44 (0)1278 760188 and choosing the technical support option.

### **TABLE OF CONTENTS**

| INTRODUCTION                                   | 6  | ) |

|------------------------------------------------|----|---|

| GETTING STARTED                                | 8  |   |

| INSTALLATION                                   |    |   |

| LEARN HOW TO USE YOUR SYSTEM                   |    |   |

| USING YOUR HECPCI9                             | 10 | ) |

| HEART                                          | 12 |   |

| Nodes                                          | 12 | , |

| Features                                       | 12 | , |

| Stage 1: Configuring HEART                     | 13 | , |

| Configurations that cannot be achieved         | 14 | Ļ |

| Inter board connection modules                 |    |   |

| Stage 2: Reading and Writing HEART connections |    |   |

| FPGA modules                                   |    |   |

| C6000 modules                                  |    |   |

| GDIO modules                                   |    |   |

| PCI bus                                        |    |   |

| HARDWARE RESET                                 |    |   |

| UDP reset                                      |    |   |

| Software Reset (Code Composer Studio)          |    |   |

| Processor JTAG connector                       |    |   |

| CONFIG                                         |    |   |

| I/Os                                           |    |   |

|                                                |    |   |

| MULTIPLE BOARD SYSTEMS                         | 21 |   |

| In same Host machine                           | 21 |   |

| Installation                                   | 21 |   |

| Accessing each board                           | 21 |   |

| IN SEPARATE HOST MACHINES                      |    |   |

| Processor JTAG                                 |    |   |

| HSB                                            | 22 | , |

| EMBEDDED SYSTEMS WITH THE HECPCI9              | 23 | , |

| Power connections                              | 23 | į |

| RESET                                          | 24 | - |

| C6000 MODULES                                  | 24 | , |

| MODULES WITH FPGA                              | 24 | , |

| GDIO MODULES                                   | 24 | - |

| HEART CONFIGURATION                            | 24 | , |

| JTAG                                           | 25 | , |

| MOUNTING THE HECPCI9                           | 25 | 1 |

| HARDWARE DETAILS                               | 27 | , |

| Power supplies                                 |    | , |

| BOARD NUMBER SWITCH                            |    |   |

| Module IDs                                     |    |   |

| HEART                                          |    |   |

| FIFO CLOCK                                     |    |   |

| Slot ordering                                  |    |   |

| Calculating Latency                            |    |   |

| Multi cast connections                         |    |   |

| FIFO flushing                                  |    |   |

| Non Blocking connections                       |    |   |

| LEDS                                           | 30 | ) |

| DEFAULT ROUTING JUMPERS                              | -  |

|------------------------------------------------------|----|

| EMBEDDED POWER CONNECTOR                             |    |

| JTAG HEADER                                          |    |

| Uncommitted Module Interconnect Connector            |    |

| INTER BOARD CONNECTION MODULE                        | 34 |

| ACHIEVABLE SYSTEM THROUGHPUT                         | 35 |

| MODULE TO MODULE COMMUNICATIONS                      |    |

| PCI COMMUNICATIONS                                   |    |

|                                                      |    |

| COMMUNICATIONS BETWEEN THE HERON SYSTEM              |    |

| HUNT ENGINEERING API                                 |    |

| USE of the API                                       |    |

| DSP SIDE SUPPORT                                     | 37 |

| COMMUNICATIONS BETWEEN HERON MODULES                 | 39 |

| PHYSICAL DIMENSIONS OF THE BOARD                     | 40 |

| FITTING MODULES TO YOUR HECPCI9                      | 41 |

| INSTALLING YOUR HECPCI9 HARDWARE                     | 42 |

| SOFTWARE                                             | 42 |

|                                                      |    |

| DSP PROGRAM                                          |    |

| HOST SIDE PROGRAMS                                   |    |

| INSTALLATION OF TOOLSAPI IDENTIFIERS FOR THE HECPCI9 |    |

| SERVER/LOADER IDENTIFIERS                            |    |

| CODE COMPOSER IDENTIFIERS                            |    |

|                                                      |    |

| TROUBLESHOOTING                                      |    |

| Hardware                                             |    |

| HOST MACHINE BIOS                                    |    |

| SOFTWARE                                             |    |

| API                                                  |    |

| Server/Loader                                        |    |

| Code Composer Studio                                 | 4/ |

| CE MARKING                                           | 48 |

| TECHNICAL SUPPORT                                    | 49 |

| APPENDIX A: DETAILS OF THE PCI INTERFACE             | 50 |

| Address Spaces and Access Modes                      |    |

| Configuration Space                                  |    |

| PCI Vendor ID and Device ID                          |    |

| Latency Timer                                        |    |

| OPERATION SPACE                                      |    |

| Offsets from the Assigned Base Address               |    |

| RESET Control                                        |    |

| FIFO Access                                          |    |

| Empty or Full FIFOs                                  |    |

| PCI Burst Transfers                                  |    |

| PCI Master Mode                                      |    |

| Interrupts                                           |    |

| Software Reset Register, offset 0380h                |    |

| General Control Register, offset 0340h               |    |

| General Status Register, offset 0340h                |    |

| General Interrupt Register, offset 0341h             |    |

| Module Information, offset 0380h                     |    |

| FIFO Data, offsets 0000h-02FFh                          | 60     |

|---------------------------------------------------------|--------|

| Inbound FIFO Flags, offset 0300h                        |        |

| Outbound FIFO Flags, offset 0301h                       | 62     |

| FIFOn Write Interrupts, even offsets 0344h-034Eh        |        |

| FIFOn Read Interrupts, odd offsets 0345h-034Fh          |        |

| Master Mode Queue Engine, offset 0360h-0377h            |        |

| Master Mode Interrupt Register, offset 0342h            |        |

| Master Mode Interrupt Mask Set Register, offset 0342h   |        |

| Master Mode Interrupt Mask Clear Register, offset 0343h |        |

| HSB Data, offset 03A0h                                  |        |

| HSB Control Register, offset 03A1h                      |        |

| HSB Status Register, offset 03A1h                       |        |

| HSB Slave Address, offset 03A2h                         |        |

| HSB Master Address, offset 03A3h                        |        |

| HSB Interrupt Register, offset 03A4h                    |        |

| HSB Timing Register A, offset 03A5h                     |        |

| HSB Timing Register B, offset 03A6h                     |        |

| JTAG Control Register, offset 0381h                     |        |

| 8990 Base Address, offset 03C0h                         |        |

| JTAG Register, offset 03E0h                             |        |

| PCI Data Test Register, offset 0320h                    |        |

| Special Test Register, offset 03F0h                     |        |

| Test Information Register, offset 03F0h                 |        |

| APPENDIX B: DEFINITION OF HEART CONTROL REGIST          | EDC 76 |

|                                                         |        |

| DIRECT SLOT ADDRESSES                                   |        |

| SECONDARY ADDRESSES                                     |        |

| COMMAND BYTE                                            |        |

| FPGA REGISTER ADDRESS                                   |        |

| Heart-to-Module FPGAs Timeslots Registers               |        |

| FIFOx Almost Empty Offset Registers                     |        |

| FIFOx UMI Reset Registers                               |        |

| UMIx Almost-Empty Register                              |        |

| Module-to-Heart FPGAs                                   |        |

| Timeslots Registers                                     |        |

| FIFOx UMI Reset Registers                               | 79     |

| UMIx Almost-Full Register                               |        |

| HEART "ZAP"                                             |        |

| FPGA REGISTER DATA BYTE                                 | 80     |

| Example                                                 | 80     |

The HERON module is a module defined by HUNT ENGINEERING to address the needs of our customers for real time DSP systems. The HERON module is defined both mechanically and electrically by a separate HERON module specification that is available from the HUNT ENGINEERING CD, via the "technology documents" section from the CD browser, or online from <a href="http://www.hunteng.co.uk">http://www.hunteng.co.uk</a> and going to the user area.

The HERON module specification also defines the features that a HERON module carrier like the HECPCI9 must provide. HERON stands for Hunt Engineering ResOurce Node, which tries to make it clear that the module is not for a particular processor, or I/O task, but is intended to be a module definition that allows "nodes" in a system to be interconnected and controlled whatever their function. In this respect it is not like the TIM-40 specification which was specific to the 'C4x DSP.

As the HECPCI9 was developed, HUNT ENGINEERING have developed HERON processor modules that carry various members of the TMS320C6000 family of DSP processors from TI, and new HERON-IO and HERON-FPGA modules. In addition to these modules, the HERON specification is a super-set of the pre-existing HUNT ENGINEERING GDIO module, so the some of the GDIO modules from our C4x product range can also be used in HERON systems.

The HERON module connects to the carrier board through several standard interfaces.

- The first is a FIFO input interface, and a FIFO output interface. This is to be used for the main inter-node communications. (It is used for this on the HECPCI9 and also for connection to the HOST PC via the PCI bus).

- The second is an asynchronous interface that allows registers etc to be configured from a HERON module. This is intended for configuring communication systems, or perhaps to control some function specific peripherals on the carrier board. (This interface is not used on the HECPCI9).

- The third is a JTAG (IEEE 1149.1) interface for running processor debug tools. (This is implemented on the HECPCI9)

- The last is the general control such as reset, power etc. (of course these are provided by the HECPCI9).

HUNT ENGINEERING defined the HERON modules in conjunction with HEART – the Hunt Engineering Architecture using Ring Technology. This is a common architecture that we have adopted for our HERON carriers. It provides good real time features such as low latency and high bandwidth, along with software re-configurability of the communication system, multicast, multiple board support etc., etc.

However, it is not a requirement of a HERON module carrier that it implements such features. In fact our customers could develop their own module carrier and add our HERON modules to it. Conversely our customers could develop application specific HERON modules themselves and add them to our systems.

The HECPCI9 implements all of the HEART features using dedicated FPGAs that cannot be considered in the same way as the FPGA on a HERON module. These have their function fixed by HUNT ENGINEERING at build time. The HECPCI9 is 6U

CompactPCI card format, interfacing to 33MHz 32bit PCI bus on J1.

The PCI interfaces to a HEART node just like the modules. This means that there are 6 FIFOs in each direction that can be connected to the HEART communications system. These FIFOs can be accessed as a PCI target interface or a 'master-mode' interface allows the hardware on the HECPCI9 to transfer data between these FIFOs and the host PC's memory without the need for the host PC's processor to copy the data.

The PCI bus also has access to the control functions such as reset, module type, Heron Serial Bus etc. These are only available as PCI target devices.

Also the PCI bus can access the JTAG test bus controller, allowing debug tools such as Code Composer to be used without external hardware.

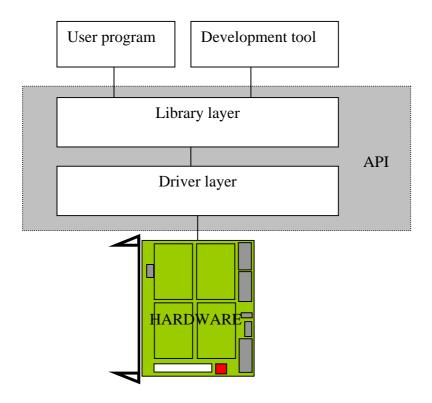

The PCI interface of the HECPCI9 should be accessed using the HUNT ENGINEERING API software, which provides a consistent interface between software tools and application programs that run on the host machine and ALL HUNT ENGINERING module carriers.

The HUNT ENGINEERING API has two implementations, a full "development and target" implementation and a "target only" implementation. The difference is that a "development and target" API supports the use of development tools, like Code Composer. This limits these Operating systems to those where Code Composer and the TI Code Generation tools will run. These are operating systems such as Win 95/98/ME and Win NT/2000/XP. A "target only" implementation is one where the Module carrier can be accessed to load and communicate with a pre-developed DSP application. In this case the HUNT ENGINEERING server/loader tool can also be provided for that operating system to enable the system to be booted and controlled. These are operating systems such as Linux, RTOS-32 etc.

For details of operating systems supported at any time please access <a href="http://www.hunteng.co.uk">http://www.hunteng.co.uk</a>

The HECPCI9 is a card that plugs into a Peripheral Slot of a CompactPCI host computer.

Any modules that your system has should be fitted to the HECPCI9 and their retaining nuts fitted, before the HECPCI9 is installed in your host machine (see a later section of this manual for details).

Normally the default routing jumpers would not be used, and software will be used to configure the connections between the nodes in your system. If you want to use the default routing jumpers see the section that discusses them later in this manual.

The PCI bus is by design a "plug 'n play" type bus, so the board is not assigned a base address by the user, but is assigned this by the host computer's PCI BIOS or operating system. After this configuration stage software can interrogate the BIOS or operating system to establish what the base addresses are.

The HECPCI9, however, provides a switch with which to select the "board number" in the system. This is the number that the API software uses to access the board. Make a note of the setting of this switch, and ensure that if you have several HECPCI9s in your system, that they all have unique switch settings.

In a PC it is necessary that the BIOS has enabled the PCI slot that you are trying to use, and that bus mastering is enabled and an interrupt is allowed for this slot. Of course all BIOS setup menus are different, and there will be different options available. The HECPCI9 requires that the slot be enabled so that the base addresses can be assigned, and that bus mastering and interrupts are enabled to allow the best performance out of any application code capable of using them.

#### Installation

The HECPCI9 should be fitted to your cCPI rack (see a later section for advice).

If the machine boots properly then follow the software installation section of the HUNT ENGINEERING CD.

If you are using Windows 95 or Windows 98/ME the operating system will detect that new hardware has been installed and will ask you for the device drivers. Choose the option that lets you continue without installing the drivers, and let the HUNT ENGINEERING software installation install the drivers.

You can follow the movie provided on how to install your system, found on the HUNT ENGINEERING CD under the Getting Started section. What this shows you how to do is:-

If you have purchased C6000 modules for your system, you will need to install Code Composer Studio at this point.

Next you should run the install option found under getting started on the HUNT ENGINEERING CD. First this program will install the HUNT ENGINEERING Application Programming Interface (API) and run the confidence checks provided with it. (See the API user manual for details).

Next it will install the HUNT ENGINEERING Software developers pack which is

required only if you have C6000 modules in your system.

#### Learn how to use your system

Then, you should follow the movie that explains HEART and how to use it. This is fundamental to being able to use the HECPCI9. The following section of this manual explains more about using HEART.

Then there are Getting started examples for C6000s and FPGAs, and tutorials about using the software tools. You should follow the tutorials that are relevant to your system to learn how to use it, and get the best use of it.

There are many examples provided on the HUNT ENGINEERING CD, and this is the best place to start developing your application program.

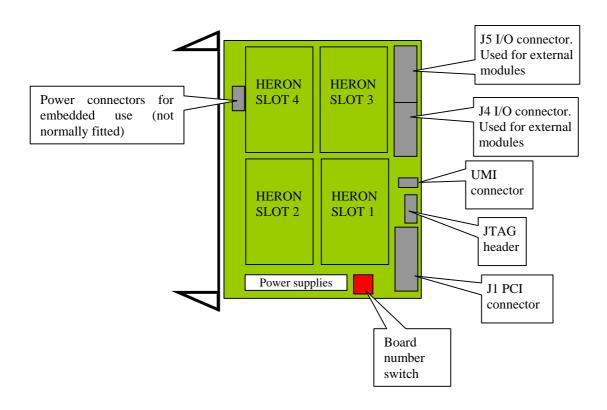

The HECPCI9 provides four HERON module sockets, each of which can be populated or left empty. Each module site can accept any 32-bit HERON module, or a subgroup of the 16-bit GDIO modules. The HECPCI9 will automatically configure for the correct module type without the need for setting any jumpers or software.

The hardware does not impose any limitation on the positions of modules, but the data paths between modules in a complicated system may only be achievable with a certain module order. In the first instance fit the modules in whatever order you like.

The connectivity of the HECPCI9 is programmable in software. Once programmed it has point to point connections between the module sites provided by virtual FIFOs. Each FIFO is 32-bits wide, but can switch into a 16 bit wide mode if a 16-bit module is detected by the hardware (see the HERON specification for details of how this is done). Each FIFO can accept a clock rate of between 60 and 100MHz, allowing a maximum transfer speed into and out of those FIFOs of 4x100Million bytes/second.

The virtual part of the FIFOS is the ring part of HEART. You do not need to know how this works, so it is not described here. If you are curious you can read the technology document from the HUNT ENGINEERING CD, via the "technology documents" section from the CD browser, or online from <a href="http://www.hunteng.co.uk">http://www.hunteng.co.uk</a> and going to the user area.

HEART allows you to connect the output FIFO from one node to the input FIFO of another, using a time slot that provides a guaranteed bandwidth. Each time slot has a bandwidth of 66.6 Million bytes/sec. If that is not enough you can allocate more than one (up to 6) time slots to that connection. Once the virtual FIFO is connected the number of time slots allocated defines the maximum achievable bandwidth through it.

In reality some other factor will define the bandwidth, perhaps the sample rate of an A/D, or the speed a processor module can process the data. It is not advisable to allocate more time slots than are needed, as the resources in a system are finite. This means that if you allocate excess bandwidth to a connection you might find that your system connectivity is impossible to achieve.

Once the virtual FIFO is connected, C6000 processor modules will access them using HERON-API, FPGA based modules will access them using the FIFO access components (VHDL) provided by HUNT ENGINEERING.

#### **HEART**

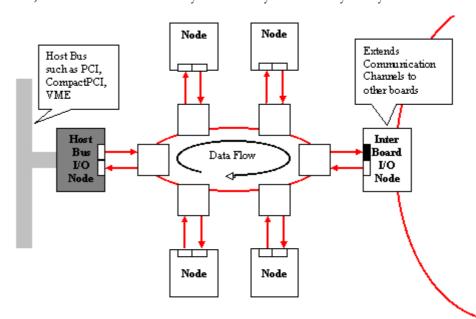

The Hunt Engineering Architecture using Ring Technology (HEART) is a novel communications system that forms the inter-node connections of the HECPCI9. It allows the connections on your HECPCI9 to be configured in software rather than the conventional use of cables that are messy, unreliable and low performance. Details of that architecture can be read elsewhere, as a user does not need to know them. Here we must describe the features it provides and how to use them.

#### **Nodes**

Your system is made up of nodes. We use that term because it does not differentiate between processor modules, FPGA modules, I/O modules, connections between boards or even Host computer connections (PCI bus interface in the case of the HECPCI9). HEART treats all of these "nodes" as equal. The HEART architecture considers each "board" to have 6 nodes, and there can be as many boards as you need in your system.

#### **Features**

HERON modules are designed to be interfaced to carrier boards that provide synchronous FIFOs.

HEART provides these FIFOs in a way that allows the FIFOs to be connected using software. We talk about these connections as virtual FIFOs, but they are in fact two FIFOs, each with one end connected to a HERON module socket and the other end connected to HEART which transports data between them.

HEART is used in two phases. The first phase is to make the connections in your system. This is equivalent to placing a phone call – not a real time operation, more of a system configuration phase.

Once the connection is made, the virtual FIFO operates exactly like a hardware FIFO, where each module uses the status flags provided at the module socket to determine if and when data can be transferred. The HEART part of that connection is transparent, and the

connection operates in real time (guaranteed bandwidth and calculable latency).

There are additional features that are useful in a real time Digital Signal Processing system such as Multi-cast data paths, FIFO flush, programmable FIFO flags etc. These are for the advanced user, and are discussed more fully later in this manual.

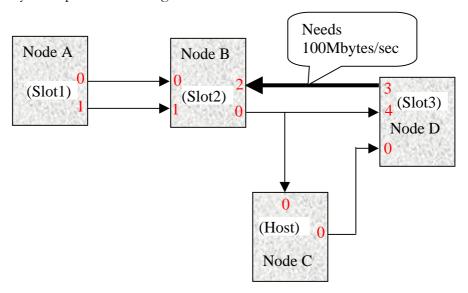

#### Stage 1: Configuring HEART

To use HEART you first need to decide the connections that you need between the nodes in your system. It is an idea to draw your system as a block diagram, where each block represents a node in your system. Now draw connections between your nodes. Each connection should represent a data or control path. There can be more than one connection between the same nodes if the system needs it, e.g. one for data flow and one for control data. Actually there can be connections that send the same data from one place to many (multi-cast). If your system needs more than 4 modules, or physically separate sub-units then you'll have more than one board in your drawing.

You must label the connections with FIFO numbers at each end. You cannot re-use the same FIFO number more than once in each direction for each node. Then choose slot numbers for each node.

So you may end up with a drawing like :-

Example of Requirements sketch.

Remember that the host PCI interface is also a node, and should be drawn in this sketch.

Notice that the choice of FIFO number is not important as long as it is not used more than once. Notice also that the FIFO number of each end does not have to be the same, and that a high bandwidth connection is still allocated only one FIFO.

Now you need to enter your connections into the "network file". Full details of this can be found in the Server/Loader user manual. The same file format is used by the Server/Loader and the heartconf utility.

An example of a file that defines the above is:-

```

# For HUNT ENGINEERING's Device Driver API use:

# BD API Board_type Board_Id Device_Id

# Using API

BD API HEP9A 0 0

# Nodes description

# ND BD_nb ND_NAME ND_Type CC-id HERON-ID filename(s)

#-----

c6

0

NodeA

ROOT

(0)

00000001

mydspprog.out

fpga

0

NodeB

normal

00000002

fpga

0

NodeD

normal

00000003

ibc 0 ibc1 normal pcif 0 NodeC normal

0x06

0 \times 0.5

#-----

# Number of the link connected to the host system

# HOSTLINK PORT

#-----

TOHOST 0

FROMHOST 0

from:slot fifo to:slot fifo timeslots

#-----

heart NodeA 0 NodeB 0

heart NodeA 1 NodeB 1

heart NodeC 0 NodeD 0

heart NodeD 3 NodeB 2

1

1

BDCAST MyData NodeB 0 1

LISTEN MyData NodeC 0

LISTEN MyData NodeD 4

```

Notice the multi-cast connection is set using BDCAST and LISTEN entries, and that the connection between Node D and Node B allocates 2 timeslots to give enough bandwidth for the 100Mbyte/sec connection.

The HeartConf or the Server/Loader program will translate this file into a set of connections.

If there is no error message then you don't need to do any more.

#### Configurations that cannot be achieved

If you receive an error message when you run HeartConf or the Server/Loader, of which there are many kinds, you need to read the message carefully to see what might be the cause.

If your message is of the type "Cannot place HEART statement....." or "Cannot place BDCAST statement..." then it may be because you have tried to use more resources than are available at a particular point in your system.

In that case you need to look at the way you have placed your nodes in the system.

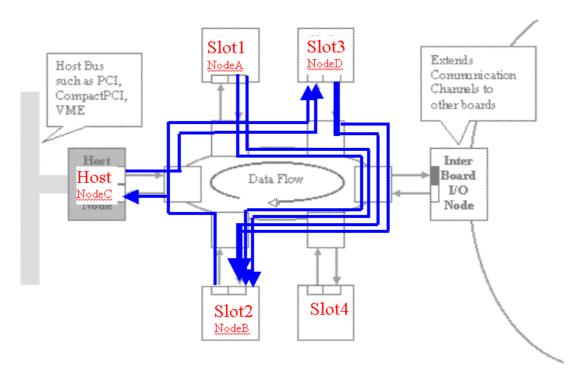

Taking our diagram of HEART, and adding the slot numbers in the order that they are connected on the HECPCI9, we can draw the connections in our example system above:-

In our case the segments that are most heavily loaded have only 4 timeslots used, so there is no problem, but you can see that moving the module from Slot 1 into Slot 4 would mean only one segment has 4 timeslots loaded. This could free up some resources for other parts of your system, which might be critical if your system was more complicated.

#### Inter board connection modules

When you have more than one board in your system, you simply draw the connections between them as connections through the inter board I/O node.

The specification of the inter board module will govern how many connections are possible and what bandwidth they support. It is normally advisable to minimise the connections between boards in the same way that we have just shown it is better to move NodeA into slot 4 above. You may find it better to move certain modules from one board to another to reduce the number of connections required.

#### Stage 2: Reading and Writing HEART connections

Once you have configured your HEART connections, they can be treated as FIFOs. These FIFOs are point to point in one direction at a time. There are flags available to determine if there is room to write data into one end, and different flags available to determine if data can be read from the other end.

Multi-cast connections are the same, just that the HEART communications system puts a copy of the data into each receiving FIFO.

By default the FIFOs operate in blocking mode. That is, if the receiver stops reading, the FIFO will eventually become full. Then the sender will not be able to write any more as the FIFO flags will indicate that there is no space.

There are some advanced options discussed later in this manual, but most users should use

the connections made in Stage1 like this – each one is essentially a single point to point FIFO.

#### FPGA modules

A HERON module that has a user configurable FPGA, has the pins of the HERON module connected to the pins of the FPGA. So the "program" for the user FPGA needs to correctly interpret the FIFO signals to access the FIFOs.

Normally this will be done using the Hardware Interface Layer that HUNT ENGINEERING provides for these modules.

The FPGA has a separate 32 bit data path for Input and Output FIFOs, so can read one FIFO and Write one FIFO at the same time. If the "Almost" flag shows that there are many things that can be done, i.e. an Input FIFO is not Almost Empty, or an Output FIFO is not Almost Full, the FPGA can transfer data at the rate of one 32bit word per FIFO clock. The FIFO clock of the HECPCI9 must be between 60 and 100MHz, so the transfer can take place at between 240 and 400 Million bytes per second. Normally the HEART connection will not be configured for this much bandwidth, so eventually the Almost flag will be asserted. Then the transfers must check the "limit" flag before each transfer. The data is then transferred more slowly than one data item per clock depending on the logic used.

The Hardware Interface Layer provided for the FPGA by HUNT ENGINEERING takes care of these things automatically, while presenting to the user a simple friendly interface.

#### C6000 modules

A HERON module with a C6000 processor will have registers where the flags of the FIFOs can be read, and separate addresses in its memory map where each FIFO can be read/written. The hardware will have features that allow the DMA engines of the processor to access these FIFOs. The users program for the processor must include the software that accesses the FIFOs using DMAs or direct processor access. The software needed will be different depending on the Module hardware design.

Normally the HERON-API software will be used to access these FIFOs, linked into the user program for the DSP.

C6000 processors usually have only one memory bus connected to the FIFOs, so it is not possible to read a FIFO and write a FIFO at the same time. That is any bus cycle can be either a read or a write but not both. Transfers can occur in both directions at once, by alternating the direction of the cycles, but this means the 240 to 400Million Bytes/second of the HERON interface is shared between reads and writes.

Usually to get the most efficient access of the FIFOs, the processor will use the "Block" flags to indicate that it is possible to transfer a block of data. On the HECPCI9 the Block flags indicate that it is possible to transfer 64 words (32 bits wide). With the right hardware on the module it is possible to DMA data on consecutive FIFO clocks during this burst, but at the end of a burst the processor will need to take some actions to enable the next burst. When the transfer size is below the block size, the processor must transfer the data one word at a time, testing the limit flag between each transfer. This means it will take at least one cycle to read the flags, and another to access the FIFO data. In reality the C6000 architecture does not allow these processor driven accesses to be achieved in a single cycle and each one may take a few tens of cycles. This makes the transfer of small blocks of data

quite inefficient. To help alleviate this problem the HECPCI9 provides "Almost" flags that are programmable. Then if a connection will always be used to transfer a small block that has a constant size, the Almost flag can be set to indicate that a transfer of that size can take place. Then the processor only has to test one flag in order to transfer the whole block.

Functions in HERON-API handle these issues for you, allowing you to use read and write calls to start transfers and then offering you a choice of ways that you can be informed when the transfer has completed. HERON-API offers you a consistent interface regardless of the hardware design of the particular module you are using.

#### **GDIO** modules

GDIO modules have a subset of the HERON module pins only. They are 16 bit modules with no user programmability. They can only access FIFO #0 of the module slot, and this access is made by the hardware of the module.

Typically GDIO module transfers cannot be blocked, and data will be lost if the FIFO reaches its limit (full or empty), but this is not always the case.

The HECPCI9 automatically detects that the module is a 16 bit version, and packs two of these 16 bit entities into each 32 bit word. The first 16 bit item is the lowest 16 bits of the 32 bit word. This is only implemented on FIFO #0 as this is the only one connected to a GDIO interface.

The "other" end of the FIFO connection will be accessed as the normal 32 bit interface.

#### **PCI** bus

The PCI bus has access to the Host node of HEART. This means that the six input and six output FIFOs can be accessed by the Host PC using the PCI bus. The PCI bus has only one data path, so it is possible to perform a read **or** a write but not both in the same cycle. Transfers can occur in both directions at once, by alternating the direction of the cycles, but this means the 133 Million Bytes/second of the PCI bus is shared between reads and writes

The Host PC can use various flags to determine how many 32 bit words can be transferred at a time. It can also use the PCI Master Mode hardware of the HECPCI9 to program hardware controlled transfers in a "DMA like" way.

The HUNT ENGINEERING Host API is usually used to access the PCI devices, as it provides the most efficient use of the PCI hardware from any of the supported Host PC operating systems. In all of these Operating Systems the software interface provided to the users program and the development tools is the same. It is even consistent between different HERON Module carriers.

#### **Heron Serial Bus (HSB)**

The HECPCI9 provides a Heron Serial Bus that runs between the Nodes. This provides a non-real time interface for configuration type messages.

On the HECPCI9 HSB is also connected to the FPGAs that implement HEART, and it is this interface that is used to configure your HEART connections. Normally HEART is configured using HeartConf or the Server/Loader tools on your Host PC. These tools access HSB using the HOST-API software to ensure that there are no resource conflicts.

It is also possible however to configure the HEART connections from a C6000 or FPGA

module. This is useful when the HECPCI9 is being used as an embedded Module Carrier, but it can also be used by "advanced" users to reconfigure your system during operation. Great care must be taken when doing this so it should not be attempted unless you understand the consequences of what you are doing.

A C6000 module would access the HSB using functions provided in the HERON-API, and an FPGA module would access HSB using the HE\_USER interface in the Hardware Interface layer provided.

HSB can be used for other system configuration or control messages, i.e. it is used by the hrn\_fpga utility to download the user configuration from the PC to an FPGA module.

It must be remembered though that the HSB is not only slow, it is also arbitrated, so it cannot be relied upon for real time operation unless your system is carefully defined so that arbitration failures will never occur.

#### **Hardware Reset**

Before the HECPCI9 can be used, it must receive a Hardware reset. Actually, the HECPCI9 generates such a reset on power up. This is generated using a CR delay so that the reset remains asserted for some time after the power supplies are stable. This is useful for when the HECPCI9 is being used "stand alone" in an embedded system.

The reset can be re-asserted via the PCI bus reset, or a register in the address space of the PCI interface.

The HOST-API function HE\_RESET allows control of this register based function.

This reset initialises all of the HECPCI9 circuitry and the modules on it into a known state. This includes disconnecting and emptying the FIFO connections between the modules.

It applies the Module Reset signal to all of the modules fitted to the HECPCI9, including inter board modules that might propagate that reset to other boards in your system.

Module Reset however does not "clear" the contents of an FPGA based module.

When the reset is asserted the LED on the back of the HECPCI9 labelled "RESET" will light up. When the reset is removed it will no longer be lit.

When running a tool like the HUNT ENGINEERING server/loader, the reset LED will flash for a short time when the system is reset prior to booting.

#### **UDP** reset

Each HERON module has a UDP reset pin that it can assert. It is not usual for a processor module to assert this, but a communications module like the HEGD7 can drive this signal. This is used to reset the board in preparation for remote booting via that communications module. The UDP reset line from each HERON module slot is simply ORed with the PCI reset to generate the hardware reset signal.

#### Software Reset (Code Composer Studio)

Code Composer Studio has a menu that allows "DSP reset". This must never be confused with the hardware reset controlled via the PCI bus – it is not the same thing. The Code Composer "DSP reset" simply resets some of the internal registers of the DSP but will NOT empty HEART FIFOs. It will also only affect the DSP where the menu is selected,

and cannot affect any I/O boards in the system.

The reset LED will not flash when a DSP reset is made from Code Composer Studio.

HUNT ENGINEERING provides a Reset Plug-in for Code Composer Studio that allows you to use the Hardware Reset from within Code Composer. This does affect all of the modules, and clear the HEART FIFOs.

#### **Processor JTAG connector**

The Processor JTAG connector is provided to allow access to the JTAG connections of the HERON modules, from an external emulator, in order to run Code Composer Studio, (the development environment for the 'C6000 processors). These connections are not used by FPGA modules, but are connected to a C6000 processor on a C6000 HERON module.

The design of the HERON module means that the HECPCI9 can determine if a HERON slot does not contain a module, or contains a module that does not implement JTAG.

The HECPCI9 hardware will therefore be automatically configured correctly for the HERON modules fitted.

Code Composer Studio needs to be configured to understand how many processors there are in the chain. When this is done please note that the hardware JTAG chain is connected to slot 1, then slot 2 then slot 3 and finally slot 4. Different versions of Code Composer Studio list these in different orders during setup so be careful when setting CCS up manually.

The connector is a standard 14 way JTAG connector as used by TI on their emulators such as the XDS510, XDS560, and also by compatible emulators from other companies. This includes the HEPC9 from HUNT ENGINEERING.

The connector on the HECPCI9 is a simple 0.1 inch header in a 7x2 configuration. It accepts the standard connector on most emulators, but beware that the C6000 JTAG chain is a 3.3V one. For this reason 5V JTAG emulators should not be used.

The JTAG header on the HECPCI9 can also be used to connect multiple boards together in the same JTAG chain. See the later sections in this manual for details on using this header.

#### Config

There is a system wide Config signal that is open collector and hence requires a pull up to be provided by the carrier board. The HECPCI9 provides this pull up. Each processor-based module will drive this signal low after a Hardware reset. It can then be released under software control after booting.

The Config signal is provided for any hardware that needs to be disabled until the entire system has booted. If there is any hardware that uses this feature it will not function until all processors have removed their config signal.

The Config is buffered and used to control an LED labelled "CONFIG" on the back of the HECPCI9. This LED will illuminate when the config signal is asserted (low).

#### I/Os

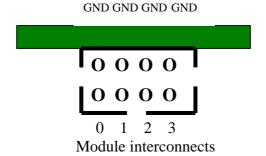

There are some "Uncommitted Module Interconnect" (UMI) signals defined by the HERON specification, which are simply connected to all modules.

These are intended to connect control signals between modules, for example a processor module can (via software) drive one of these signals with one of is timer outputs. Then if an I/O or FPGA module is configured to accept its clock input from one of these signals, it is possible to implement a system with a programmable clock. There will be other uses for these signals that are module design dependent.

The HECPCI9 pulls these signals high with 10K resistors.

The HECPCI9 also connects these four signals to the UMI connector near the rear edge of the board.

You can fit multiple HECPCI9s into your system. They can be in the same Host PC, or in separate machines or racks. Usually these multiple boards will be connected using an Inter board module. The specification of that module will define what is and is not possible, but as a minimum it will be possible to route HEART connections to and from that Inter board module, which will be connected by that module to the other Module carrier in your system.

#### In same Host machine

In the case where you are installing more than one HECPCI9 in the same Host PC, all you need to remember is to set the red board switch to a different setting on each board.

#### Installation

The HOST-API will access multiple boards in your system. The recommended way to install multiple boards is to begin by installing a single board only. When that installation has completed and all the confidence checks have passed, then you can shut down your PC and fit the other boards. When the system is powered up the new boards should be detected and the drivers installed. It is then advisable to use the Confidence checks from the Programs \rightarrow HUNT ENGINEERING \rightarrow group to check each board individually.

#### Accessing each board

When installation is completed, the PCI bus will have allocated separate resources to each board. These boards can be accessed using HOST-API.

To specify which board to access the "Board number" variable in the open calls to HOST-API need to be set to the same setting that you selected on the Board switch of that board.

#### In separate Host machines

When the boards of your system are in separate host PCs, it is still a good idea to choose different board numbers, in case the inter board modules you have connect the HSB. HSB uses a combination of the Board number and the slot number to form its addresses.

#### **Processor JTAG**

The HECPCI9 JTAG header allows you to connect multiple boards together in the same JTAG chain. It is not always necessary to do this as Code Composer can be run separately on each board, but if you want to run a single Code Composer session across multiple boards you need to connect the JTAG chain as one single chain.

The JTAG header on the HECPCI9 can be used as an input or an output – selected via the PCI bus. On reset the HECPCI9 configures the JTAG chain to be a slave of the JTAG header, i.e. the header is an input, and it is used to drive the JTAG paths of the HECPCI9.

When the HOST-API resets the HECPCI9 the board is set to use the on board circuitry to control the JTAG chain. This is the "normal" mode of operation.

In the multiple board situation you need to set the first board as a Master board, and have the following boards as slaves. For details of how to do that see the Windows HOST-API user manual.

Note that the "default" after reset is to be a slave of the JTAG header – the setting required by all except the first board in your system. This allows the multiple board JTAG to be supported even if the host PC does not have access to the JTAG switch on those boards. An example of this is using a Master board in a PC to debug an embedded board that has no connection to a PCI bus.

#### **HSB**

The HSB can be connected between multiple boards in a system, but that would be a capability of the Inter board module. Refer to the user documentation of your particular Inter board module for details.

#### **Embedded systems with the HECPCI9**

The HECPCI9 can be used as an embedded HERON module carrier. In this case there are no connections to the PCI bus necessary. The HEART will run to provide communications and the modules will operate just the same as when the assembly is fitted to a PC.

#### **Power connections**

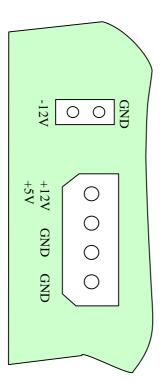

There are optional power connectors provided on the HECPCI9 that allow the power supplies needed to be powered via cables and connectors. The main connector provides +5V and +12V using a standard PC Disk drive connector. The HECPCI9 uses only the +5 power and generates +3.3V and +2.5V from this. The +12V is used by some modules but not all – check the user manuals for each module for details.

Very few modules use -12V, so normally it is enough to use just the Disk drive type connector, but there is a separate connector for -12V is that is necessary in your system.

The connections to the connectors are marked clearly on the PCB:-

Normally these connectors are not fitted to the HECPCI9, but if you request it they can be fitted at the factory, otherwise you can fit them yourself.

If fitted at the factory, the larger connector would be AMP part number 350211-1 (the same as is fitted to a PC disk drive). A suitable mating connector is AMP 1-480424 with crimp AMP 1-480426-0.

The smaller connector would be fitted with a latching KK type connector Molex part number 22-04-1021. A suitable mating connector is Molex 22-01-1023 with crimp type 08-50-0032.

#### Reset

The HECPCI9 automatically generates a reset signal following power up. This means that the system will be properly initialised if you simply "switch on" the power.

If you feel the need for an external reset signal, there is a small 2-pin jumper above the J1 connector on the HECPCI9. It is misleadingly labelled JTAG, but is in fact a reset input. The connector its pin 2 connected to ground. The other pin, pin 1, (identified with the silk-screen square around it), is an input to the PCI FPGA on the HECPCI9, pulled to 3.3V with a 10K resistor. When the two pins are connected together the HECPCI9 will be reset, but the same can be achieved by driving a logic signal onto this connector. A low level is taken as a reset.

There is a certain amount of de-glitching applied to this signal to allow the direct connection of a switch that might exhibit some contact bounce. Any low level of less than 100nS will be ignored. After the low level is detected the reset will be held low for approximately 0.2S. Any low pulses during that time will re-start the timing of the 0.2S.

#### C6000 modules

A C6000 HERON module boots the processor from some on board FLASH ROM. Normally this is a pre-boot that initialises the hardware and starts to accept a boot stream from a FIFO.

In an embedded system there is no way to boot your application program onto the module using the FIFOs. In this case you must program your application into the on board FLASH ROM. Utilities and instructions that help you do this can be found on the HUNT ENGINEERING CD.

#### **Modules with FPGA**

Modules that have FPGAs can have PROMS fitted to them that initialise the FPGA with your application program. You need to refer to the user manual of the particular module that you are using for details of the options provided and how to use them.

#### **GDIO** modules

GDIO modules do not require any programming but are simply hardware that starts to run after reset.

#### **HEART** configuration

Even in an embedded system the HEART connections need to be initialised. Simple systems might be able to use the Default Routing Jumpers discussed in a later section of this manual.

Most systems however will need to "nominate" a module in the system to perform this initialisation.

A C6000 module can use the HERON-API functions to access the HSB, and hence have the HEART initialisation embedded in the application software.

A module with an FPGA can use the HE\_USER interface in the Hardware Interface Layer to initiate HSB messages. In this way the HEART configuration can be stored in a ROM component in the FPGA.

#### **JTAG**

The HECPCI9 defaults to using the JTAG header as an input that will master the JTAG chain. Hence an embedded HECPCI9 can accept a JTAG input from another HECPCI9 or a TI XDS510 or XDS560 without requiring any further set up.

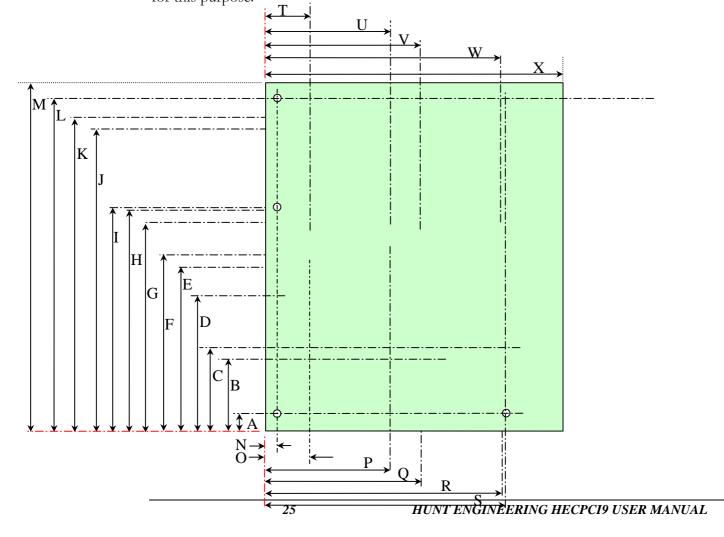

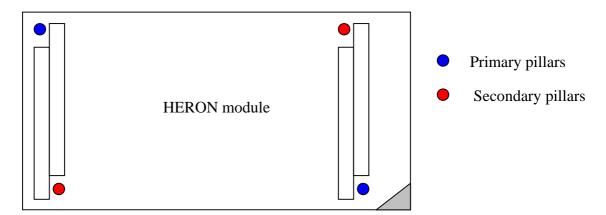

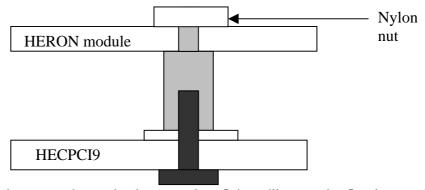

#### **Mounting the HECPCI9**

The HECPCI9 is supplied with hardware for fitting it into a CompactPCI host machine. This can be removed when the board is to be embedded. Two screws hold front panel.

When these have been removed, the fixing holes can be used to mount the HECPCI9 in your system. Because of the height of the HECPCI9 it is also recommended that one or more fixings are used in the centre of the board. The Module Fixing positions can be used for this purpose.

| Reference | Description                                      | Dimension  |

|-----------|--------------------------------------------------|------------|

| A         | Bottom edge to lower panel fixing                | 5.5 mm     |

| В         | Bottom edge to Slots 1 and 2 top outer fixing    | 37.5 mm    |

| С         | Bottom edge to Slots 1 and 2 top inner fixing    | 42.5 mm    |

| D         | Bottom edge to lower centre panel fixing         | 94.5 mm    |

| Е         | Bottom edge to Slots 1 and 2 bottom inner fixing | 115 mm     |

| F         | Bottom edge to Slots 1 and 2 bottom outer fixing | 120 mm     |

| G         | Bottom edge to Slots 3 and 4 bottom outer fixing | 132.77 mm  |

| Н         | Bottom edge to Slots 3 and 4 bottom inner fixing | 137.77 mm  |

| I         | Bottom edge to upper centre panel fixing         | 138.85 mm  |

| J         | Bottom edge to Slots 3 and 4 top inner fixing    | 210.27 mm  |

| K         | Bottom edge to Slots 3 and 4 top outer fixing    | 215.27 mm  |

| L         | Bottom edge to upper panel fixing                | 227.85 mm  |

| M         | Board height                                     | 233.35 mm  |

| N         | Left edge to panel fixings                       | 3.57 mm    |

| О         | Left edge to Slot 2 right side fixings           | 18.726 mm  |

| P         | Left edge to Slot 2 left side fixings            | 72.726 mm  |

| Q         | Left edge to Slot 1 right side fixings           | 84.776 mm  |

| R         | Left edge to Slot 1 left side fixings            | 138.776 mm |

| S         | Left edge to rear optional mounting holes        | 140.07 mm  |

| Т         | Left edge to Slot 4 left side fixings            | 17.226 mm  |

| U         | Left edge to Slot 4 left side fixings            | 73.226 mm  |

| V         | Left edge to Slot 3 right side fixings           | 85.266 mm  |

| W         | Left edge to Slot 3 right side fixings           | 139.266 mm |

| X         | Board length                                     | 160 mm     |

The following sub-sections provide details on the hardware such as connector pinouts and signal levels etc, but they are placed here, as the "system" configurer does not normally need this information. It is, however, necessary for a user who needs to develop compatible hardware or for use in system troubleshooting.

#### **Power supplies**

The HECPCI9 is a 6U CompactPCI peripheral board. It is a 5V only card as defined by the CompactPCI specification – it makes no connection to the backplane 3.3V supply. Connection IS made to the +12V and –12V supplies, for possible use by modules, although the HECPCI9 does not use these supplies itself.

| Voltage | Typical (& measured) | Maximum |

|---------|----------------------|---------|

| +5V     | 2.7A                 | 4.0A    |

| +12V    | 0                    | 0       |

| -12V    | 0                    | 0       |

Remember when calculating system power that the power requirements of each module must be added to these.

#### **Board Number Switch**

The only user configurable option on the HECPCI9 is the board number switch. This switch can be turned by hand and a hexadecimal number between 0 and F is displayed to indicate its current setting.

The number selected by this switch is the "board number" that must be used when accessing this board using the HUNT ENGINEERING API software. This is achieved by the driver layer of the API reading the switch value, and using this to identify this card to the upper layers of the API.

The value of this switch is also used by the HERON processing modules when they are booted. This is to make sure that they do not boot from data intended for another processor. Refer to the user manual of the relevant HERON processing module for details.

The HSB also uses the board number setting to address the nodes.

There is no restriction on the setting of this switch other than there cannot be two boards on the same PCI bus with the same setting of this switch.

#### Module IDs

Each node of the HECPCI9 has a slot number assigned to it, as defined in the HERON specification. The combination with the Board number switch and this slot ID allows the module to identify itself uniquely in the system.

The boot prom of the HERON processing modules use this for boot purposes as does the HSB for addressing particular nodes.

| Node               | Slot ID assigned |

|--------------------|------------------|

| HERON slot 1       | 1                |

| HERON slot 2       | 2                |

| HERON slot 3       | 3                |

| HERON slot 4       | 4                |

| Host node          | 5                |

| Inter board module | 6                |

| HEART devices      | 7                |

#### **HEART**

How to use HEART is described in the earlier sections of this manual.

How HEART works is described for the interested reader in a separate technical document that can be found on the HUNT ENGINEERING CD. Please note that it is not necessary to understand how HEART works – this is just background information.

#### FIFO CLOCK

The FIFO clocks on the HECPCI9 are according to the 100MHz FIFO timings shown in the HERON module specification. The clock has a minimum frequency of 60MHz and a maximum frequency of 100MHz.

The clocks from each module, and the read and write clocks can all have different frequencies with any phase relationship.

#### Slot ordering

To make the signal routing on the HECPCI9 simpler and reliable the HEART devices are connected in an order that is perhaps not what you expected. The HEART is connected as :-

$\rightarrow$  Host node  $\rightarrow$  Slot1  $\rightarrow$  Slot3  $\rightarrow$  Inter board node  $\rightarrow$  Slot4  $\rightarrow$  Slot2  $\rightarrow$  Host node

This should not affect how you use HEART, but is sometimes important to understand if your system configuration uses a lot of resources.

It is also important to understand this ordering if you need to calculate the Latency between nodes.

#### **Calculating Latency**

One feature of HEART is that the latency of a communication is controlled within limits that can be calculated. The way that the connections of HEART are pre-connected means that there are no arbitration delays. It is also not possible that a connection will fail to connect – it is already connected before the data is sent.

The use of FIFOs means that the latency varies depending on how you use them. For example if you use a block flag to determine when to write, that write may be delayed until there is space.

If we consider the simple case of using the limit (full and empty) flags, and a connection that has no data in either FIFO, we can calculate the limits of the latency as follows:-

- 1. Writing a data item to the FIFO will take two FIFO clocks.

- 2. That data will be available to the HEART system after 13 cycles of 100MHz

- 3. The time slots travel around the HEART ring constantly, so the longest wait for a slot will be five 100MHz clocks, the data will be placed onto the ring in the sixth clock at the latest.

- 4. The data is clocked around the ring constantly, and takes 4 clocks to pass through each node that is not receiving the data. For the sending node it takes one clock to be passed on, and on the receiving node it takes one clock to be received.

- 5. The data is written into the FIFO on the next 100MHz clock.

- 6. That data will flow through the FIFO, in 6 cycles of 100MHz,

- 7. The Empty flag will be set after 3 cycles of the FIFO clock.

- 8. The data item can be read on the next FIFO clock.

i.e. items 1, 7 and 8 make a total of 6 clock cycles at the FIFO clock. Items 2,3,4,5 and 6 make a total of 20+(4\*number of nodes passed)+(up to 5) clock cycles at 100MHz.

Any inter-board connections will add to this latency, the exact amount will be dependent on the module design. Refer to the user documentation of the module for a precise definition.

The calculations above show that there is a very small amount of uncertainty, and even if we take the maximum spread that we can achieve with a single board we see:-

Adjacent slots using maximum FIFO clocks (minimum latency): 260ns to 310ns

From slot to itself using minimum FIFO clock frequency (maximum latency) 500ns to 550ns.

#### Multi cast connections

It is possible to use "special" connections with HEART, where more than one receiver can receive the data sent by one node. This is achieved because the receiver of a time slot does not destroy the data, it continues around the HEART.

As you can see from the earlier sections of this manual this is achieved by specifying the sender and each receiver separately in the network file for your system.

#### FIFO flushing

A special feature of the HEART is that the FIFOs in a connection can be cleared by a module asserting one of its UMI lines. In that case the clearing event is programmed for a FIFO using the HSB configuration registers. Multiple FIFOs can be programmed to "flush" on the same UMI line, so sending and receiving halves of the same connection can be cleared, or even, multiple connections cleared without asserting the hardware reset.

Normally this feature will be selected by the HEART configuration tool. Once this setting is selected for a particular FIFO, the flushing can take place by writing the UMI as an output from a C6000 module or simply driving the UMI line from an FPGA.

For definitions of those registers see the appendix of this manual.

#### Non Blocking connections

Another feature of HEART is to allow receivers to "listen" to a connection but not block that connection if the FIFO becomes full. This can be useful if the sender has no way of stopping the transmission, or if the node is simply monitoring data and it does not matter if data is lost. Often this will be used in conjunction with the FLUSH feature.

This selection is also made via the HSB control registers in the HEART device, and is also normally selected by the HEART configuration tool.

For definitions of those the HSB registers see the appendix of this manual.

#### **LEDS**

There are many LEDS on the reverse side of the HECPCI9, most of them are used to indicate if the FPGAs that form the HEART are properly configured from their PROMS.

Next to each FPGA that should flash briefly on power up, but then remain off. This shows that the FPGA has configured. If at any time one of these LEDs is illuminated, try powering your system off (that is switch off, not re-boot) and back on again. If the LED is still illuminated then there is a hardware fault and you should contact Technical support at your supplier.

At the front edge of the board, on the reverse side, there are five more LEDS:

Two of these LEDS are labelled 2.5V and 3.3V. These are normally illuminated to indicate that their respective power supply circuits are functioning. If either of these is not illuminated then the Power supply is not working. This could be because you short-circuited a connection and the safety feature has activated to prevent damage to your hardware. If at any time one of these LEDs is **not** illuminated, try powering your system off (that is switch

off, not re-boot) and back on again. If the LED is still **not** illuminated then there is a hardware fault and you should contact Technical support at your supplier.

There is another LED labelled "SYNC LOSS". This is illuminated if the HEART ring is receiving corrupted control data. This normally indicates that there is a failure of the hardware. If at any time one of these LEDs is illuminated, try powering your system off (that is switch off not re-boot) and back on again. If the LED is still illuminated then there is a hardware fault and you should contact Technical support at your supplier.

The remaining two LEDs are indicators of the state of the Reset and Config lines. They are labelled "RESET" and "CONFIG" and illuminate when the respective signal is asserted (low).

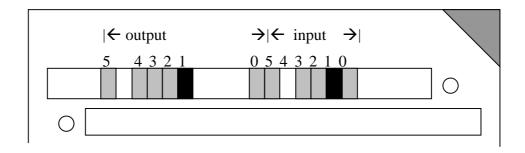

#### **Default Routing Jumpers**

The default routing jumpers are provided by HERON modules and GDIO modules as built for use in HERON systems. These are the longer pins on the topmost HERON connector of the module. These pins protrude above the HERON/GDIO module when it is fitted to the HECPCI9 to which jumper links can be fitted.

On the HECPCI9 these jumpers are used to select which the connections of timeslots to FIFO #0 following a hardware reset.

For example with the jumpers as fitted in the diagram, Input FIFO#0 will be receive data from time slot 1, and Output FIFO#0 will write data to time slot 1.

If more than one jumper is fitted at the same time then all of those time slots will be used by FIFO#0, to form a higher bandwidth connection.

When using the development tools supplied with the HECPCI9 it is not necessary to use the default routing jumpers at all. Any connections required by the tools will be configured by them in software, and the connections that you define in your network file will then be configured for you by that tool. In fact the default setting on Heartconf and the Server/Loader is to disconnect any default connections before making its own connections. If you want to disable this feature it is necessary to disable HEART zapping in the tool you are using.

The default routing jumpers can be useful in a small number of cases if the system requires only simple connections. If all connections can be made using FIFO #0, then using the default routing jumpers can remove the need to configure HEART. This is not sensible in a C6000 system using Server/Loader as that will make its own connections for booting which may clash with your selections. Really this is useful in a simple embedded system.

#### **Embedded Power connector**

The embedded power connector is not normally fitted to the HECPCI9. It is not necessary when the HECPCI9 is fitted to a host PC as the power is connected using the PCI connector in that case.

It is intended to simplify the use of an HECPCI9 in an embedded system. The details are described in the earlier sections of this manual that discusses embedded use of the HECPCI9.

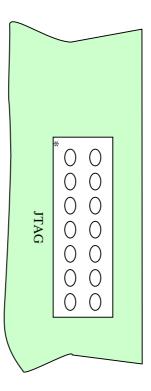

#### JTAG header

There is a 14 way JTAG header on the HECPCI9, just above the J1 PCI connector.

This connector is the standard pinning for a 14 way JTAG header so it accepts the cable supplied with a TI XDS510 or 560 for example.

| TMS     | * O | О | TRST         |

|---------|-----|---|--------------|

| TDI     | O   | O | GDN          |

| PD      | O   |   | Polarisation |

| TDO_RET | О   | O | GND          |

| TCK_RET | O   | O | GND          |

| TCK     | O   | O | GND          |

| EMO0    | O   | O | EMU1         |

|         |     |   |              |

The same connector can be used to drive JTAG signals so that a one to one cable can be used to connect between two HECPCI9s. In this case the "mode" of this connector must be set differently on each of the boards.

The "Mode" is set to use this connector as an input that drives the JTAG chain of the modules, following each hardware reset.

The Test Bus Controller on the HECPCI9 can be used to master just its own modules, or its own modules and the slave board(s) via this connector. In this case this connector is used as an output.

The Mode is selected via the PCI bus, normally using Host API functions.

For details of the registers see the PCI appendix of this manual.

All of the signals are protected against Electro Static Discharge and over voltage to 3.3V. The devices used are Harris SP723 parts.

This protects the inputs to IEC1004-2 level 4, and provides over voltage limiting to the range 0 to +3.3V.

#### **Uncommitted Module Interconnect Connector**

As per the HERON module specification there are four signals that are connected between the HERON modules. They are uncommitted in that they serve no fixed purpose, but HERON modules can provide functions that use these signals.

For example a HERON processor module might drive one of its timers onto one of these signals. A HERON-IO module might then be configured to use this as its sample clock.

In such an example it is easy to see that the same timer could be used to provide the sample clock of a HERON-IO module on another board.

For these reasons the four uncommitted Module interconnect signals are provided unbuffered on a connector on the HECPCI9. This is situated on the rear edge of the board between the two Compact PCI connectors. It is a 2mm pitch connector that is angled to accept its cable "flush" with the pcb. This connector is a MOLEX type 877333-0820, which requires MOLEX type 50394 crimp terminals together with MOLEX type 51110-0860 crimp housing for the cable termination.

The pin out is as follows

These signals are pulled high by a 10K resistor to 3.3V on the HECPCI9.

All of the signals are protected against Electro Static Discharge and over voltage to 3.3V. The devices used are Harris SP723 parts.

This protects the inputs to IEC1004-2 level 4, and provides over voltage limiting to the range 0 to +3.3V.

#### Inter Board connection module

Inter-board modules for the HECPCI9, do not connect directly with the HECPCI9. Instead, the connections between the HECPCI9 and CPCI9-EM2 are made via the J4 and J5 CompactPCI connectors, when a CPCI9-EM2 is fitted to the rP4 and rP5 connectors on the rear side of the backplane, as a Rear Panel I/O board.

The inter-board modules are specific to the HECPCI9 and are used to provide inter board connections using a HEART node. Connections may be made between multiple HECPCI9s, and HEPC9s.

To reduce the build cost of the HECPCI9 there are not dedicated HEART devices on the HECPCI9 for this module. The Ring data is simply pipelined past the slot when no interboard module is fitted. In this case extra registers are inserted into the ring at that position to maintain the right number of data items on the ring.

When a module is fitted to this slot, those pipeline registers are disabled and the ring data is passed through the inter board module. In that case an FPGA on the module provides the correct pipeline so that the number of registers on the ring has not changed.

The specification of this external module will not be published, and all inter board modules will be designed and manufactured by HUNT ENGINEERING.

For this reason the dimensional and electrical details of this interface do not need to be discussed here.

#### **Achievable System Throughput**

In a HERON system there are many factors that can affect the achievable system throughput. It must be remembered at all times that the part of the system that has the lowest limit on bandwidth will govern the throughput of the system.

The FIFOs on the HECPCI9 are 32 bits wide, and have a maximum clock rate of 100MHz. This leads to a bandwidth limit of 400Million bytes/second. The HEART connection between the ends of the FIFOS will be made using timeslots that provide increments of 66Million bytes/second.

#### **Module to Module Communications**

The clock for the FIFO is generated by the HERON or GDIO module, so in fact this 400Million bytes/second will not be achieved unless the module provides the maximum clock frequency of 100MHz, AND the module performs accesses in consecutive clock cycles.

For the bandwidth that will be achieved in each connection in your system you must check the bandwidth limits of the modules at each end of the FIFO as well as the limit of the FIFO.

This module to module communication should use the HERON-API software supplied by HUNT ENGINEERING to protect user software.

Examples when using two HERON4 modules with HERON-API are:-

1 timeslot 66Mbytes/sec with dedicated DMA, 51Mbytes/sec with non-dedicated

3 (or more) timeslots 232Mbytes/sec with dedicated DMA, 113Mbytes/sec with non-dedicated

For more detailed discussions of this topic please refer to the HUNT ENGINEERING web site.

#### **PCI Communications**

The PCI communications throughput is dependent on the Xilinx design for the HECPCI9, the API drivers and libraries, and the Host PC performance.

The Xilinx has been designed to be capable of 132Mbytes/second peak on the PCI bus.

It has also been designed to use the PCI Master Mode, and allow queuing of transactions so that the PCI bus can be utilised almost all of the time even when the Host Operating system is responding to interrupts etc.

An example of a P3-800 running windows NT is 65Mbytes/sec (one timeslot) 100Mbytes/sec with 3 or more timeslots. This can be affected by the host operating system as well as things like the processor/memory speed of the PC or even the PCI chipset used.

For more detailed discussions of this topic please refer to the HUNT ENGINEERING web site.

## Communications Between the HERON System & the Host PC

The host computer connection to the HECPCI9 is the PCI bus. The PCI interface of the HECPCI9 has been implemented in a custom FPGA.

#### **HUNT ENGINEERING API**

The Host computer side of the HECPCI9 PCI interface is fully supported by the HUNT ENGINEERING API software, which consists of a driver layer and a library layer. This software comes free of charge with your hardware – see the HUNT ENGINEERING CD for the software, the installation utilities and the documentation.

The Library layer provides an interface to the development tools and user "host side application" programs which is the same simple interface for all HUNT ENGINEERING hardware.

The driver layer provides an interface that is optimised for each operating system, and host board.

Thus the API provides an interface between the hardware and "host side" software that remains the same regardless of hardware type or revision, and also regardless of operating system.

This brings you a well-supported interface coupled to maximum performance for those

operating systems that the HUNT ENGINEERING API supports. (see the separate API user manual).

HUNT ENGINEERING will support you fully if you use the API, but cannot guarantee to help you if you attempt to provide your own device driver support. If you require support for an operating system that is not currently supported by the API then please contact us for advice -- we would prefer to add standard support to the API for you than to support you writing your own drivers. Of course there are limited resources for doing this so we reserve the right to decline.

#### **USE of the API**

The API uses a simple asynchronous communications model, which we briefly discuss here – for full details refer to the latest HUNT ENGINEERING API user manual.

First the device must be claimed by performing an Heopen () on the device. This function takes a board identifier, (hep9a in the case of the HECPCI9), a board number (as set by the board number switch) and a device number. In the case of the HECPCI9 there are eight devices:-

| description | Device number |

|-------------|---------------|

| FIFO A      | 0             |

| FIFO B      | 1             |

| JTAG        | 2             |

| HSB         | 3             |

| FIFO C      | 6             |

| FIFO D      | 7             |

| FIFO E      | 8             |

| FIFO F      | 9             |

The function returns a file descriptor if the call is successful, or else an API error code.

If the system is to be booted, a reset must be performed using Hereset() on the file descriptor given by the open call.

A write to the FIFO can be started using the Hewrite() function on the file descriptor.

A read from the FIFOS can be started using the Heread() function on the file descriptor.

Both the read and write functions will return immediately, with either a successful status, an in-progress status or an error. The in-progress status allows the host side application to continue processing of previous data while the hardware access is taking place.

The status of an I/O can be tested at any time using the HEestforIO() function, or the host program can be blocked until it is complete by using the HEwaitforIO() function.

## **DSP** side support

The DSP module accesses the DSP side of the HOST FIFOS in exactly the same manner as

## **Communications between HERON Modules**

The HERON modules communicate using the HEART FIFO connections that have been configured.

Each type of HERON processor module will have its own method of addressing the FIFOS, so it is important to use the HERON-API software provided with the hardware. This software comes free of charge with your hardware – see the HUNT ENGINEERING CD for the software, and the documentation.

The HERON-API follows a similar method to the host side API, bringing a standard set of functions to manage your inter-module communications in the most efficient way supported by your hardware.

The HERON-API determines which HERON module the functions should be compiled to use by a simple #include in the DSP program.

Again an asynchronous model is used allowing a communication to be requested and processing of previous data to continue while the communication takes place. To achieve this processor DMA is used wherever possible.

See the separate documentation on the HERON-API for details.

# **Physical Dimensions of the Board**

The HECPCI9 is 233.35mm by 160mm overall, and is supplied with a standard CompactPCI front panel.

The 0mm limit on component height of motherboard components under the module site is not violated by the HECPCI9.

The maximum height of the components on the back of the HECPCI9 is 2mm.

Fitting HERON modules to your HECPCI9 is very simple.

Ensure that the HECPCI9 does NOT have power applied when fitting modules, and normal anti-static precautions should be followed at all times.